gmail.com-blog-RK3399 MIPI LCD

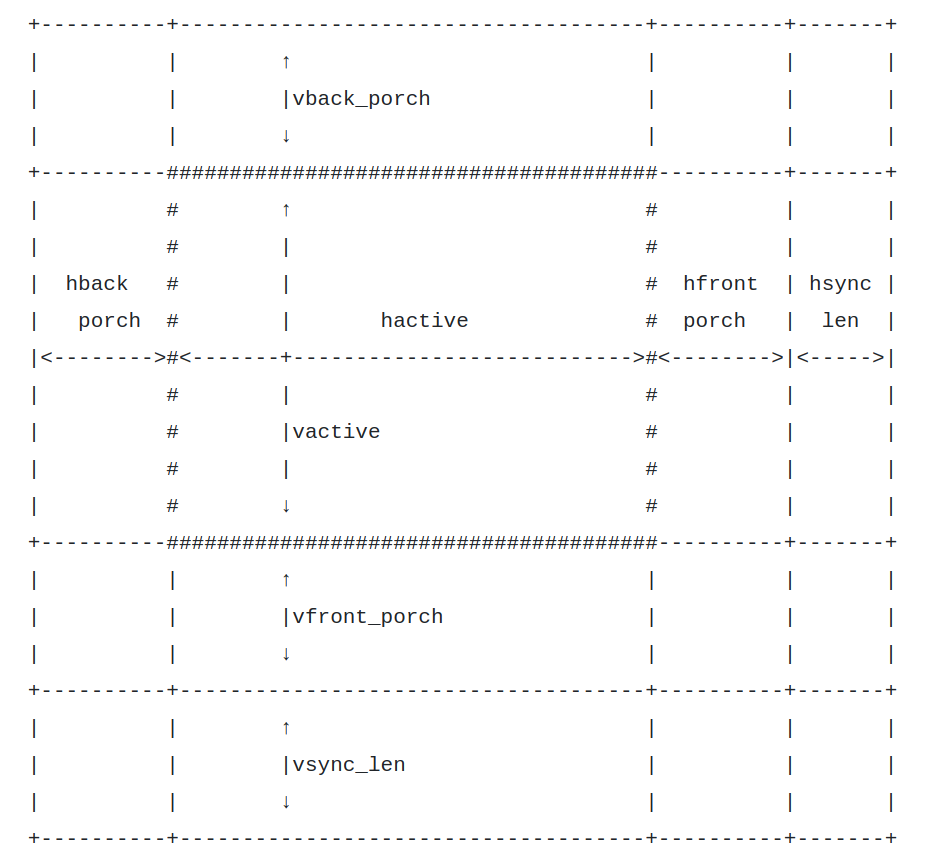

rockchip-display-timing

DTS

&dsi0 {

status = "okay";

rockchip,lane-rate = <480>;

panel: panel {

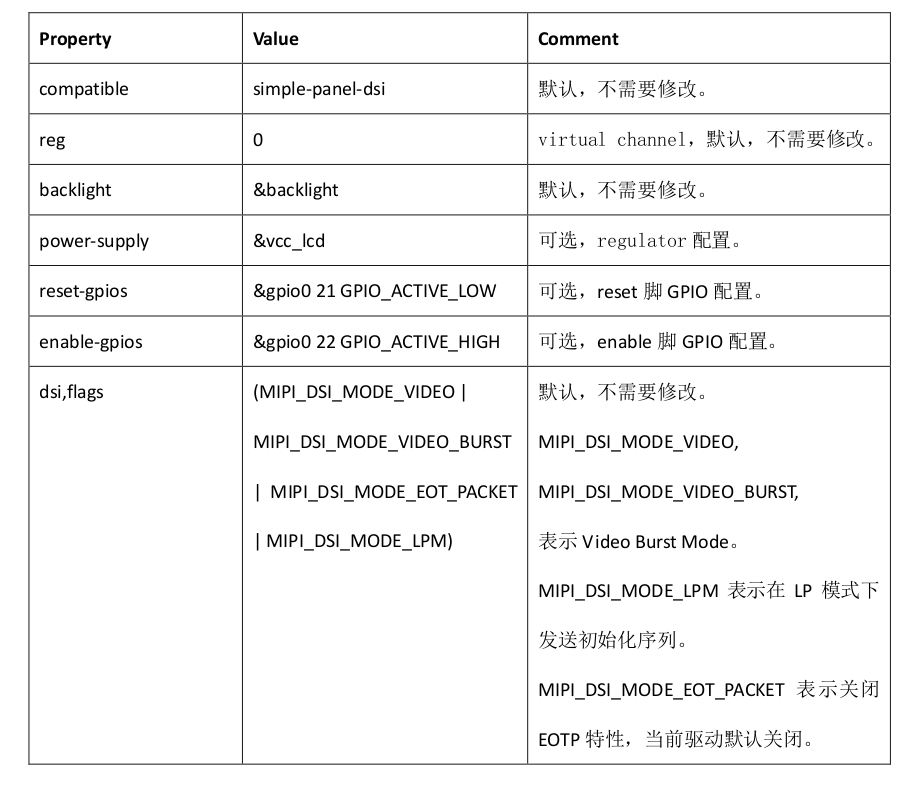

compatible = "simple-panel-dsi";

reg = <0>;

backlight = <&backlight>;

reset-gpios = <&gpio7 3 GPIO_ACTIVE_LOW>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST | MIPI_DSI_MODE_LPM)>;

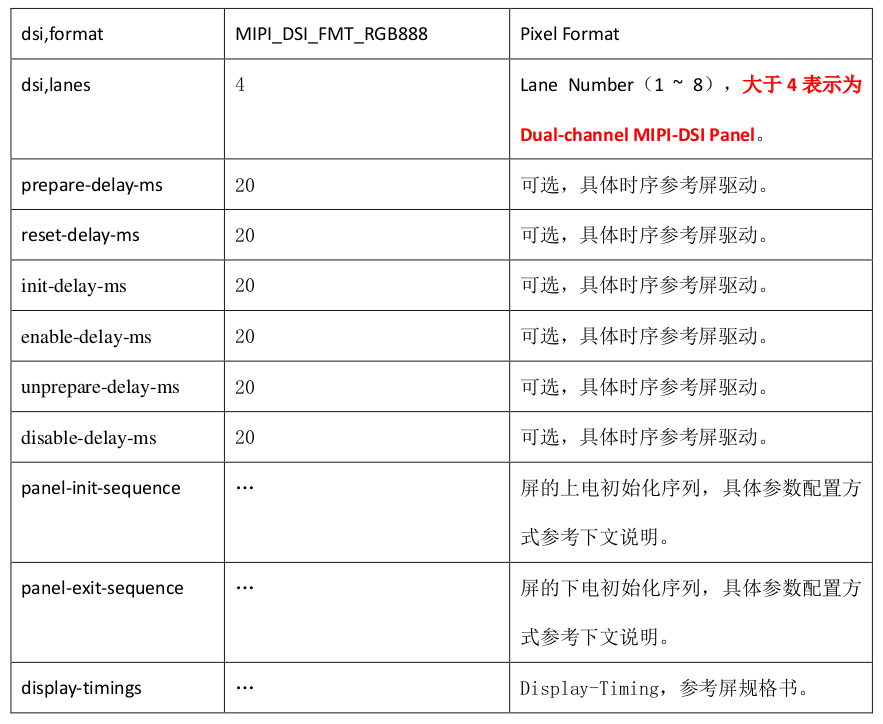

dsi,format = <MIPI_DSI_FMT_RGB888>;

dsi,lanes = <4>;

bus-format = <MEDIA_BUS_FMT_RBG888_1X24>;

reset-delay-ms = <30>;

init-delay-ms = <120>;

enable-delay-ms = <30>;

prepare-delay-ms = <30>;

unprepare-delay-ms = <30>;

status = "okay";

panel-init-sequence = [

39 00 03 F0 5A 5A

39 00 03 F1 A5 A5

39 00 03 F0 B4 4B

39 00 03 C2 83 10

39 00 0D B0 ba 98 ba 98 33 33 33 33 2a 00 84 00

39 00 09 B1 93 94 02 89 2a 01 84 01

39 00 12 B7 01 01 09 11 0D 15 19 0D 21 1D 00 00 20 00 02 ff 3c

39 00 07 BD 4E 0E 4B 4B 20 1A

39 00 06 B8 24 01 30 34 55

39 00 06 C7 05 23 6B 49 00

39 00 09 C6 00 00 FF 00 00 FF 00 00

39 00 04 C3 22 61 04

39 00 17 B3 1C 1C 05 05 07 07 1D 1D 23 03 22 22 03 13 13 11 11 0F 0F 0D 0D 00

39 00 17 B4 1C 1C 04 04 06 06 1D 1D 23 03 22 22 03 12 12 10 10 0E 0E 0C 0C 00

39 00 04 d0 07 ff ff

39 00 05 D2 63 0B 08 88

39 00 27 C8 7E 60 52 45 42 32 37 22 3C 3B 3B 5B 4B 54 47 44 37 25 0C 7C 62 52 46 42 32 37 22 3B 3B 3A 5B 4B 54 47 44 37 25 0C

05 78 01 11

05 32 01 29

];

panel-exit-sequence=[

05 78 01 28

05 78 01 10

];

disp_timings: display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <69900000>;

hactive = <800>;

vactive = <1280>;

hback-porch = <20>;

hfront-porch = <16>;

vback-porch = <12>;

vfront-porch = <16>;

hsync-len = <4>;

vsync-len = <4>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

};

};

&route_dsi0 {

status = "okay";

};

MIPI param

初始化序列

15 00 02 80 77

| | | | |

| | | | 数据

| | | | 寄存器地址

| | 数据长度

| 延时

命令类型(0x05: 单字节数据 0x15: 双字节数据 0x39: 多字节数据)

DCS_Long_Write_3P(0xFF,0x98,0x81,0x01)————39 00 04 FF 98 81 01 DCS_Short_Write_1P(0x01,0x00) ——————–15 00 02 01 00 DCS_Short_Write_NP(0x11)————————–05 78 01 11

步骤

- 分辨率

- 接口 dsi,lanes = <4>;

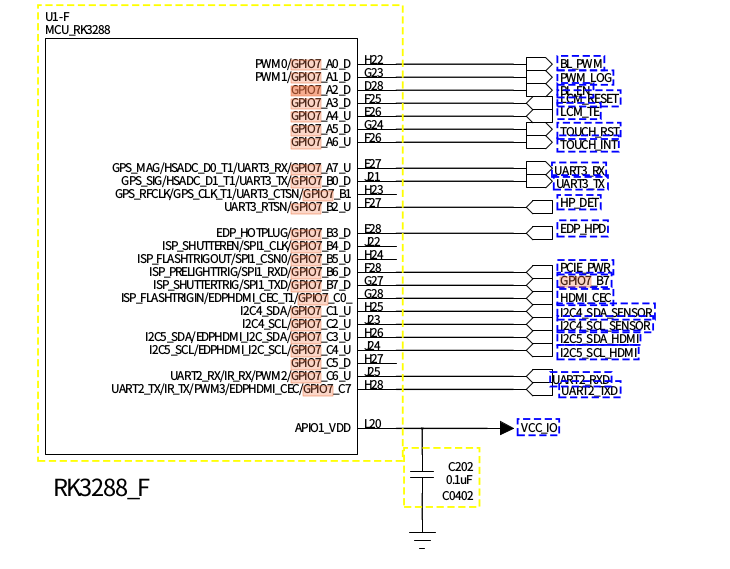

- 看原理图,管脚配置 reset-gpios = <&gpio7 3 GPIO_ACTIVE_LOW>;

- disp_timings 配置

- 初始化序列配置

- 背光配置

BL_EN 和 LCM_RESET

LCD_EN : enable-gpios = <&gpio8 3 GPIO_ACTIVE_HIGH>; LCD_RESET : reset-gpios = <&gpio7 3 GPIO_ACTIVE_LOW>; BL_EN : enable-gpios = <&gpio7 2 GPIO_ACTIVE_HIGH>;

驱动代码

kernel/drivers/gpu/drm/rockchip/dw-mipi-dsi.c

调试

$ cat d/dri/0/summary

VOP [ff930000.vop]: DISABLED

VOP [ff940000.vop]: ACTIVE

Connector: DSI

overlay_mode[0] bus_format[100e] output_mode[0] color_space[0]

Display mode: 800x1280p61

clk[68000] real_clk[68000] type[8] flag[a]

H: 800 816 820 868

V: 1280 1285 1289 1292

win0-0: ACTIVE

format: AB24 little-endian (0x34324241) SDR[0] color_space[0]

csc: y2r[0] r2r[0] r2y[0] csc mode[0]

zpos: 0

src: pos[0x0] rect[800x1280]

dst: pos[0x0] rect[800x1280]

buf[0]: addr: 0x01046000 pitch: 3200 offset: 0

win1-0: DISABLED

win2-0: DISABLED

win2-1: DISABLED

win2-2: DISABLED

win2-3: DISABLED

win3-0: DISABLED

win3-1: DISABLED

win3-2: DISABLED

win3-3: DISABLED

post: sdr2hdr[0] hdr2sdr[0]

pre : sdr2hdr[0]

post CSC: r2y[0] y2r[0] CSC mode[1]

0

次点赞