Rockchip_Developer_Guide_Ethernet_CN.pdf

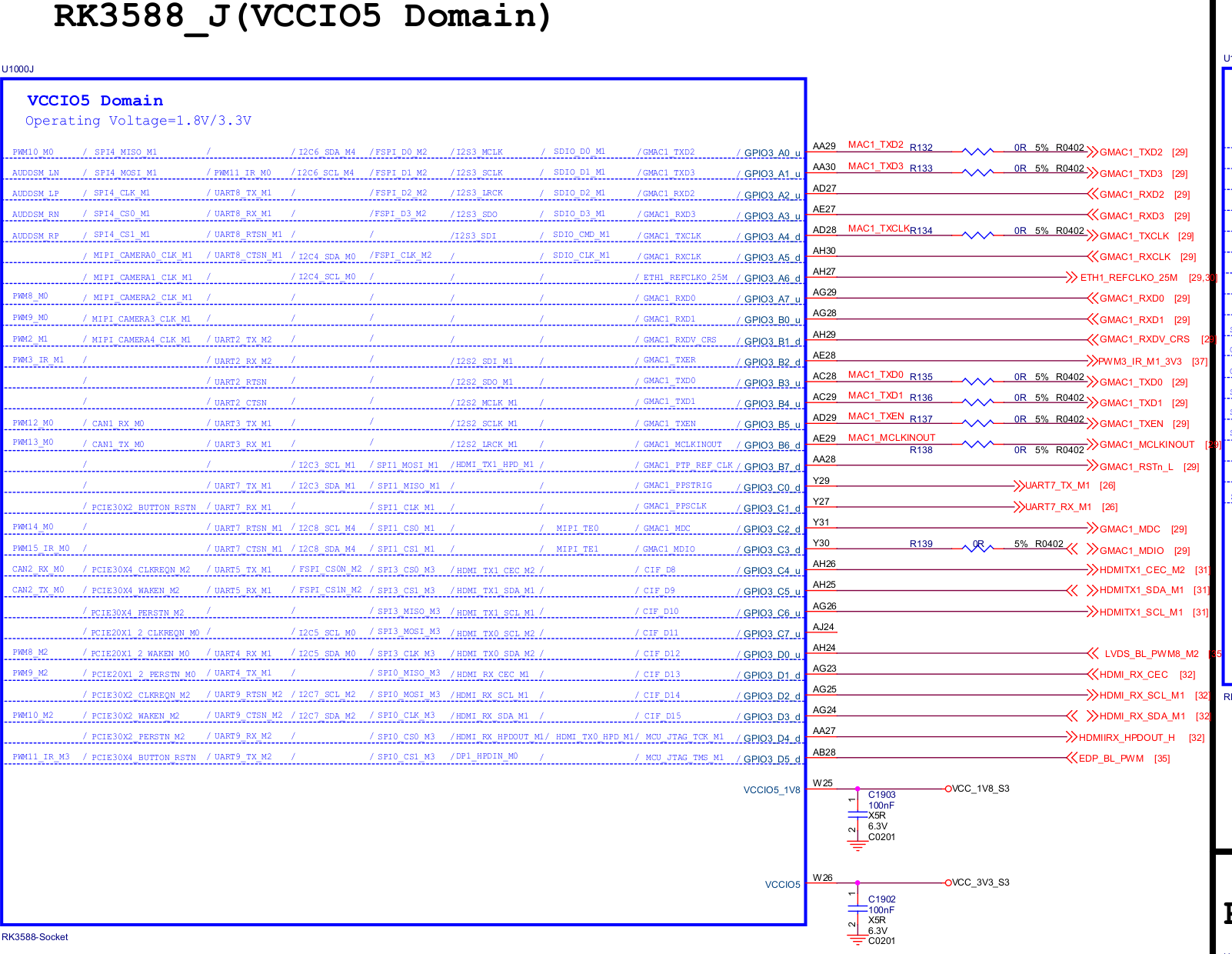

硬件

由于在 RK 系列的 SoC 中内置了以太网 MAC 控制器,所以只需要搭配一颗以太网 PHY 芯片,即可实现以太网卡功能。按照规范,即使是不同厂家的 PHY,仍然有一部分寄存器的定义是通用的,只要配置了这些通用的寄存器,基本上 PHY 就可以正常工作。因此,在 Linux 驱动中有通用的 PHY驱动,RK3288 之前的芯片所配套的 SDK 中使用的都是通用驱动,当然 SoC 中的 MAC 驱动是需要实现的。所以理论上,如果不需要使用 PHY 厂家提供的自定义的寄存器配置实现一些个性化的功能,那么 PHY 的驱动就不需要修改。

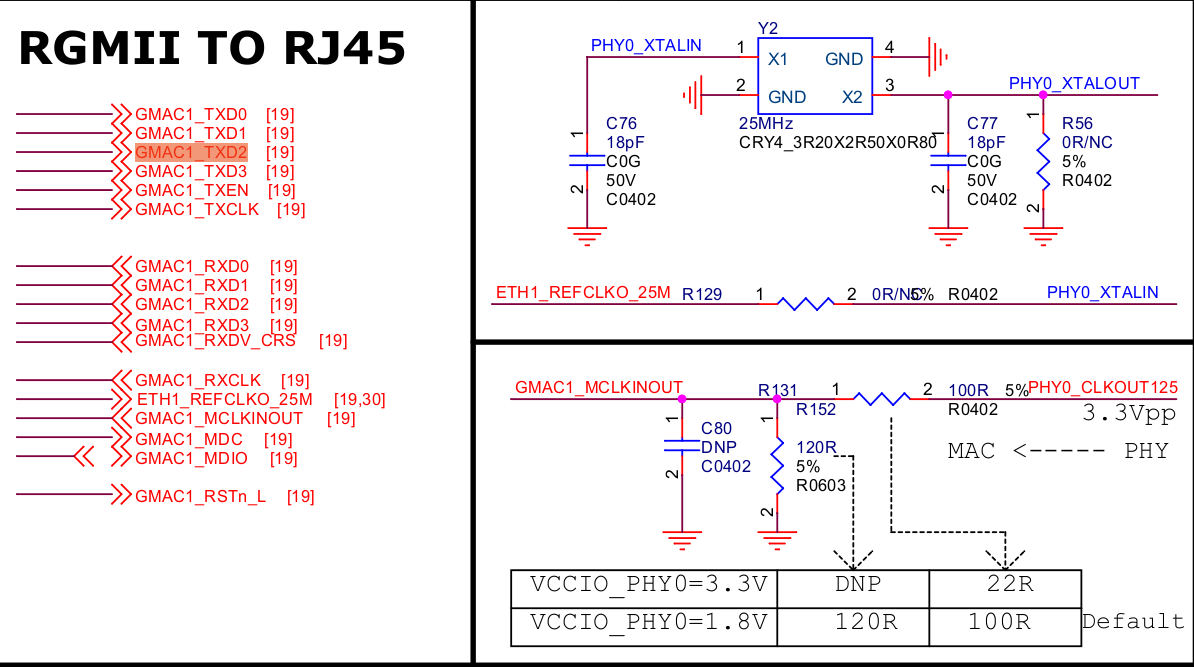

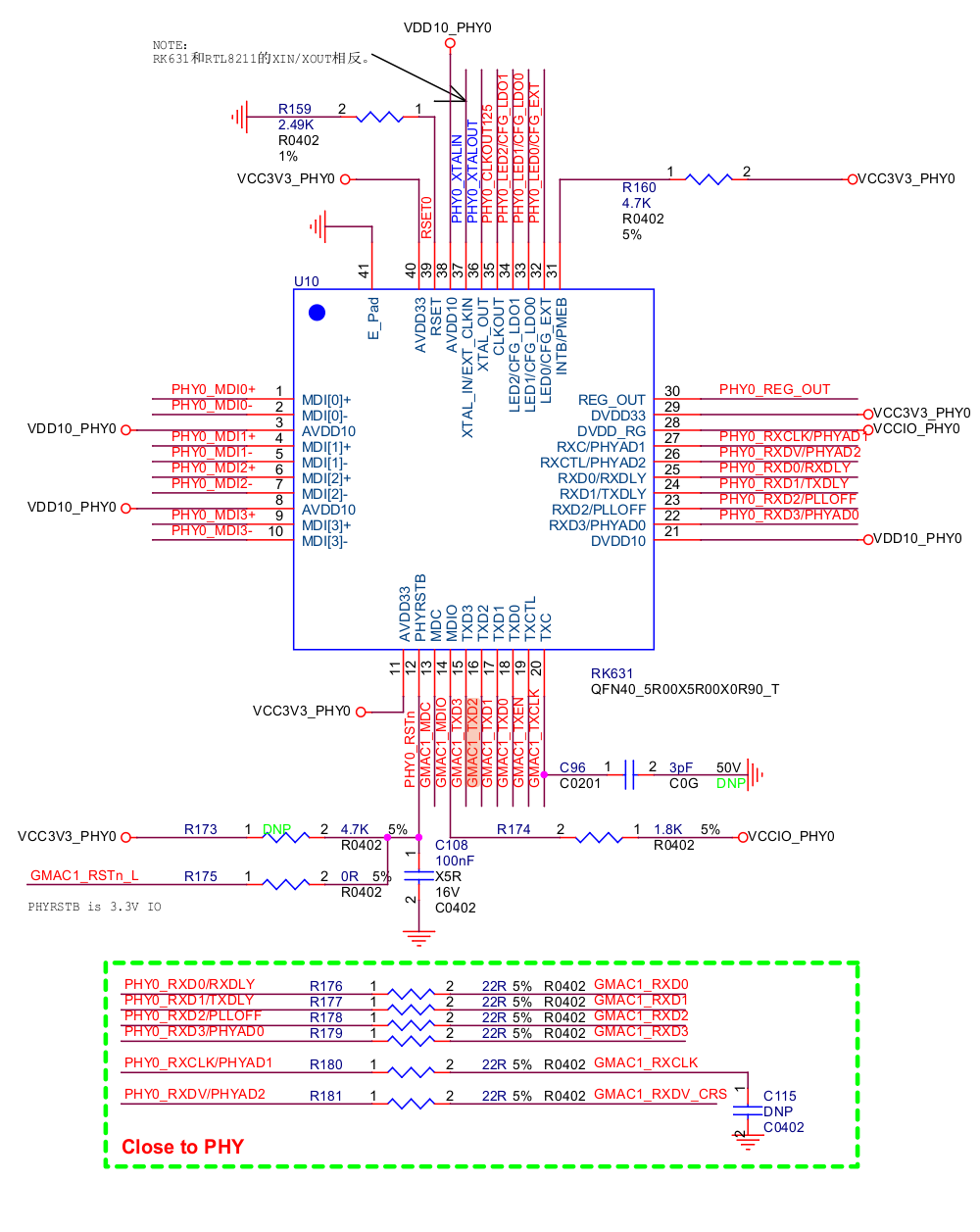

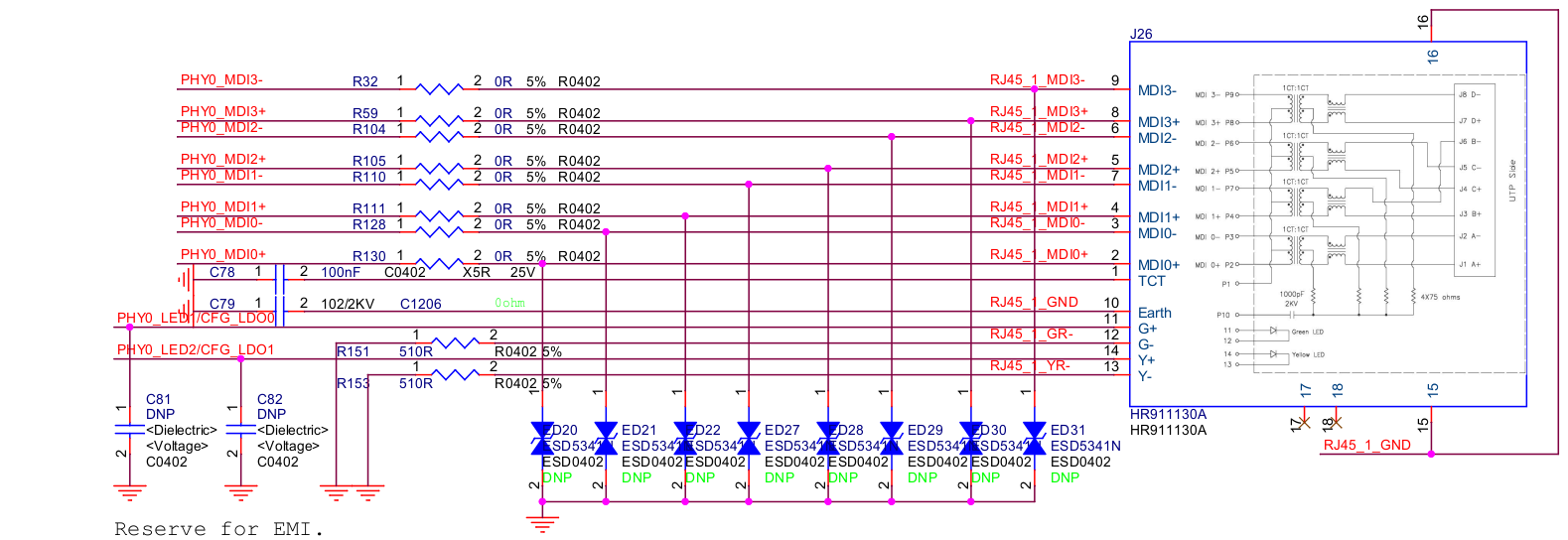

RTL8211F

RGMII TO RJ45

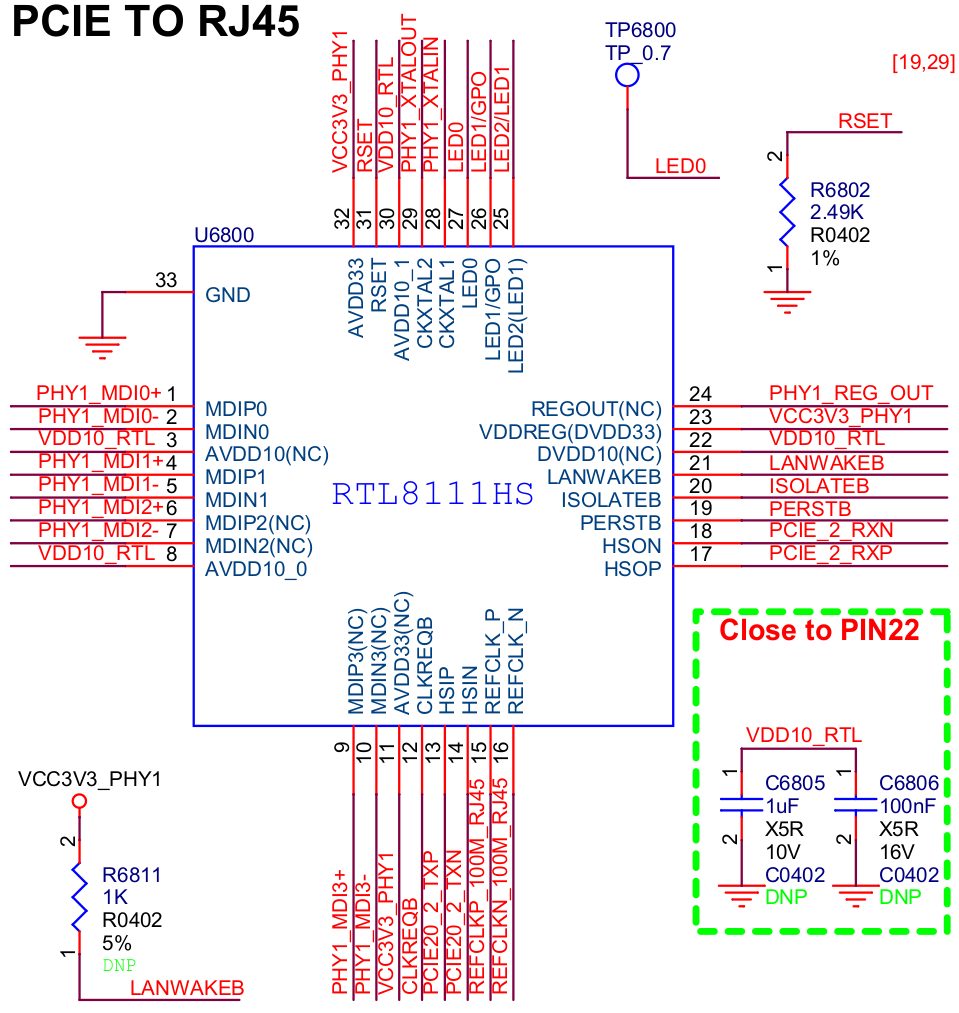

PCIE TO RJ45

RTL8211F 驱动

rk3588.dtsi

gmac1: ethernet@fe1c0000 {

compatible = "rockchip,rk3588-gmac", "snps,dwmac-4.20a";

reg = <0x0 0xfe1c0000 0x0 0x10000>;

interrupts = <GIC_SPI 234 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 233 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "macirq", "eth_wake_irq";

rockchip,grf = <&sys_grf>;

rockchip,php_grf = <&php_grf>;

clocks = <&cru CLK_GMAC_125M>, <&cru CLK_GMAC_50M>,

<&cru PCLK_GMAC1>, <&cru ACLK_GMAC1>,

<&cru CLK_GMAC1_PTP_REF>;

clock-names = "stmmaceth", "clk_mac_ref",

"pclk_mac", "aclk_mac",

"ptp_ref";

resets = <&cru SRST_A_GMAC1>;

reset-names = "stmmaceth";

power-domains = <&power RK3588_PD_GMAC>;

snps,mixed-burst;

snps,tso;

snps,axi-config = <&gmac1_stmmac_axi_setup>;

snps,mtl-rx-config = <&gmac1_mtl_rx_setup>;

snps,mtl-tx-config = <&gmac1_mtl_tx_setup>;

status = "disabled";

mdio1: mdio {

compatible = "snps,dwmac-mdio";

#address-cells = <0x1>;

#size-cells = <0x0>;

};

gmac1_stmmac_axi_setup: stmmac-axi-config {

snps,wr_osr_lmt = <4>;

snps,rd_osr_lmt = <8>;

snps,blen = <0 0 0 0 16 8 4>;

};

gmac1_mtl_rx_setup: rx-queues-config {

snps,rx-queues-to-use = <2>;

queue0 {};

queue1 {};

};

gmac1_mtl_tx_setup: tx-queues-config {

snps,tx-queues-to-use = <2>;

queue0 {};

queue1 {};

};

};

&gmac1 {

/* Use rgmii-rxid mode to disable rx delay inside Soc */

phy-mode = "rgmii-rxid"; /* 主要分为 RMII(百兆) 和 RGMII(千兆) 模式 */

clock_in_out = "output";

snps,reset-gpio = <&gpio3 RK_PB7 GPIO_ACTIVE_LOW>; /* PHY 的硬件复位脚 */

snps,reset-active-low;

/* Reset time is 20ms, 100ms for rtl8211f */

snps,reset-delays-us = <0 20000 100000>;

pinctrl-names = "default";

pinctrl-0 = <&gmac1_miim

&gmac1_tx_bus2

&gmac1_rx_bus2

&gmac1_rgmii_clk

&gmac1_rgmii_bus>;

tx_delay = <0x43>;

/* rx_delay = <0x3f>; */

phy-handle = <&rgmii_phy>;

status = "okay";

};

kernel-5.10/drivers/net/ethernet/stmicro/stmmac/dwmac-rk.c

static const struct of_device_id rk_gmac_dwmac_match[] = {

#ifdef CONFIG_CPU_RK3588

{ .compatible = "rockchip,rk3588-gmac", .data = &rk3588_ops },

#endif

};

MODULE_DEVICE_TABLE(of, rk_gmac_dwmac_match);

static struct platform_driver rk_gmac_dwmac_driver = {

.probe = rk_gmac_probe,

.remove = rk_gmac_remove,

.driver = {

.name = "rk_gmac-dwmac",

.pm = &rk_gmac_pm_ops,

.of_match_table = rk_gmac_dwmac_match,

},

};

module_platform_driver(rk_gmac_dwmac_driver);

MODULE_AUTHOR("Chen-Zhi (Roger Chen) <roger.chen@rock-chips.com>");

MODULE_DESCRIPTION("Rockchip RK3288 DWMAC specific glue layer");

MODULE_LICENSE("GPL")

RTL8111H 驱动

pcie2x1l0: pcie@fe170000 {

compatible = "rockchip,rk3588-pcie", "snps,dw-pcie";

#address-cells = <3>;

#size-cells = <2>;

bus-range = <0x20 0x2f>;

clocks = <&cru ACLK_PCIE_1L0_MSTR>, <&cru ACLK_PCIE_1L0_SLV>,

<&cru ACLK_PCIE_1L0_DBI>, <&cru PCLK_PCIE_1L0>,

<&cru CLK_PCIE_AUX2>, <&cru CLK_PCIE1L0_PIPE>;

clock-names = "aclk_mst", "aclk_slv",

"aclk_dbi", "pclk",

"aux", "pipe";

device_type = "pci";

interrupts = <GIC_SPI 243 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 242 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 241 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 240 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 239 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "sys", "pmc", "msg", "legacy", "err";

#interrupt-cells = <1>;

interrupt-map-mask = <0 0 0 7>;

interrupt-map = <0 0 0 1 &pcie2x1l0_intc 0>,

<0 0 0 2 &pcie2x1l0_intc 1>,

<0 0 0 3 &pcie2x1l0_intc 2>,

<0 0 0 4 &pcie2x1l0_intc 3>;

linux,pci-domain = <2>;

num-ib-windows = <8>;

num-ob-windows = <8>;

num-viewport = <4>;

max-link-speed = <2>;

msi-map = <0x2000 &its0 0x2000 0x1000>;

num-lanes = <1>;

phys = <&combphy1_ps PHY_TYPE_PCIE>;

phy-names = "pcie-phy";

ranges = <0x00000800 0x0 0xf2000000 0x0 0xf2000000 0x0 0x100000

0x81000000 0x0 0xf2100000 0x0 0xf2100000 0x0 0x100000

0x82000000 0x0 0xf2200000 0x0 0xf2200000 0x0 0xe00000

0xc3000000 0x9 0x80000000 0x9 0x80000000 0x0 0x40000000>;

reg = <0x0 0xfe170000 0x0 0x10000>,

reg-names = "pcie-apb", "pcie-dbi";

resets = <&cru SRST_PCIE2_POWER_UP>, <&cru SRST_P_PCIE2>;

reset-names = "pcie", "periph";

rockchip,pipe-grf = <&php_grf>;

status = "disabled";

pcie2x1l0_intc: legacy-interrupt-controller {

interrupt-controller;

#address-cells = <0>;

#interrupt-cells = <1>;

interrupt-parent = <&gic>;

interrupts = <GIC_SPI 240 IRQ_TYPE_EDGE_RISING>;

};

// PCIE TO RJ25

&pcie2x1l0 {

reset-gpios = <&gpio1 RK_PB4 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&rtl8111_isolate>;

status = "okay";

};

&pinctrl {

rtl8111 {

rtl8111_isolate: rtl8111-isolate {

rockchip,pins = <1 RK_PB4 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

}

以太网参数

eth1 Link encap:Ethernet HWaddr ec:0a:81:96:f0:b4 Driver r8168(驱动)

inet addr:192.168.0.56 Bcast:192.168.0.255 Mask:255.255.255.0

inet6 addr: fe80::b0be:3214:ee84:81f2/64 Scope: Link

UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1

RX packets:108581 errors:0 dropped:0 overruns:0 frame:0

TX packets:18963 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:129120381 TX bytes:1152927

Interrupt:154 Base address:0xf000

接口名称和地址:

- 接口名称 (eth1):这是指定的以太网接口名称。

- MAC地址 (HWaddr ec:0a:81:96:f0:b4):设备的物理地址,用于在局域网中唯一标识设备。

- IPv4地址 (inet addr: 192.168.0.56):设备分配的IPv4地址。

- 广播地址 (Bcast: 192.168.0.255):IPv4广播地址,用于向本地网络上的所有设备发送消息。

- 子网掩码 (Mask: 255.255.255.0):确定哪些IP地址属于本地网络的一部分。

IPv6地址:

- IPv6地址 (inet6 addr: fe80::b0be:3214:ee84:81f2/64):设备的IPv6地址和子网前缀。

接口状态和配置:

- 接口状态 (UP BROADCAST RUNNING MULTICAST):接口当前状态为上线(UP),并且支持广播和多播传输。

- MTU (MTU: 1500):以太网接口的最大传输单元,表示在不进行分段的情况下可以发送的最大数据包大小。

- 接口度量 (Metric: 1):指示网络跃点(hop)的数量或跳数。通常用于路由决策。

数据包统计和错误:

- 接收数据包数 (RX packets: 108581):自接口启动以来接收的数据包总数。

- 接收错误 (errors: 0):接收过程中发生的错误数。

- 接收丢包 (dropped: 0):由于缓冲区溢出或其他原因而丢弃的接收数据包数。

- 发送数据包数 (TX packets: 18963):自接口启动以来发送的数据包总数。

- 发送错误 (errors: 0):发送过程中发生的错误数。

- 发送丢包 (dropped: 0):由于缓冲区溢出或其他原因而丢弃的发送数据包数。

- 发送冲突 (collisions: 0):在发送过程中检测到的碰撞次数。

- 发送队列长度 (txqueuelen: 1000):发送队列的长度,表示可以缓冲的待发送数据包数。

数据传输量:

- 接收字节数 (RX bytes: 129120381):自接口启动以来接收的总字节数。

- 发送字节数 (TX bytes: 1152927):自接口启动以来发送的总字节数。

0

次点赞