职位介绍

核心工作: 电路设计, PCB设计, EMC 整改

三大工具: 万用表, 示波器, 电烙铁

辅助工具: 信号发生器, 可调直流稳压电源, 功率计等

必备能力:

- 电子电路知识

- 信号阻抗, PCB

- EMC

- 结构

- 软件

- 创新

5 可原则

- 可预测

- 可设计

- 可测量

- 可复用

- 可传承

岗位职责

- 元器件选型

- 设计电路图

- 信号完整性仿真

- PCB板卡设计

- 焊接和调试

- 协助软件工程师测试

- EMC测试

电子工程师素养

- 扎实的电子电路知识和设计功底

- 了解电子电气的相关标准

- 深化专业领域的学习

- 跨学科知识和技能的了解

- 多实践, 多总结

- 创造力和想象力

电子硬件通用知识

电子设备电源

电能质量偏差

相电压 和 线电压的概念

380(220)V AC 等级线路允许的电压偏差为+7%, -10%, 最高有效电压为235.4V AC

AC-DC 电源模块转换的常见电压 48V DC, 24VDC, 12V DC, 5V DC.

3.3V DC 和 1.8V DC 是设备内部芯片使用的电压

电压偏差范围

支持3.3V 供电的元器件, 数据手册上的供电电压范围一般是3.0-3.6V

无论是轻载还是满载, 各级直流电压上的交流电压分量(纹波电压)都应该小于30mV

人体安全电压

正常是36V, 但是不同的环境安全电压不同

设备地

金属外壳设备, 220V AC供电设备要接PE(地线), 防止触电

电子设备温度

温度等级

汽车级: -55°C ~ 125°C 工业级: -40°C ~ 85°C 商业级: 0°C ~ 70°C

焊接温度的影响

一般电烙铁的温度要比焊锡丝的熔点温度高50°C才可以, 手动焊接时, 夏天的推荐温度为320°C, 冬天推荐温度为350°C, 单个焊点焊接时间应该小于3s

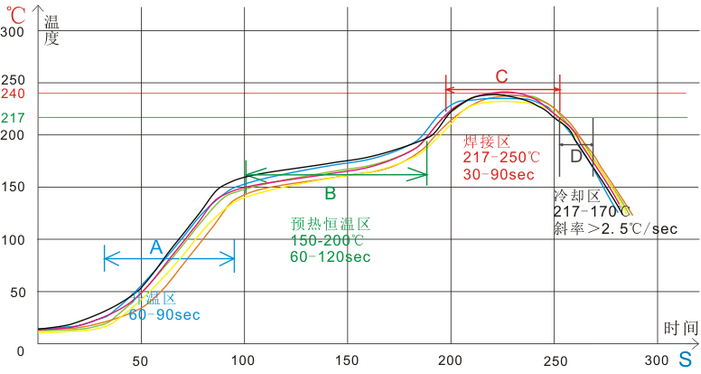

回流焊(贴片元件) 和 波峰焊(插件元件)

焊接炉温曲线

炉温曲线选择不恰当, 会导致焊接元器件的管脚不光亮, 偏暗, 容易虚焊, PCB板卡有锡珠现象

案例: 温度影响时钟偏差, 如何选择时钟芯片(晶振)

电子芯片电平

芯片拉电流: 输出时芯片流出电流 芯片灌电流: 输出时芯片流入电流

芯片I/O引脚输出阻抗

芯片相同的I/O引脚在高电平输出, 低电平输出时的阻值是有差异的

逻辑电平的转换方法

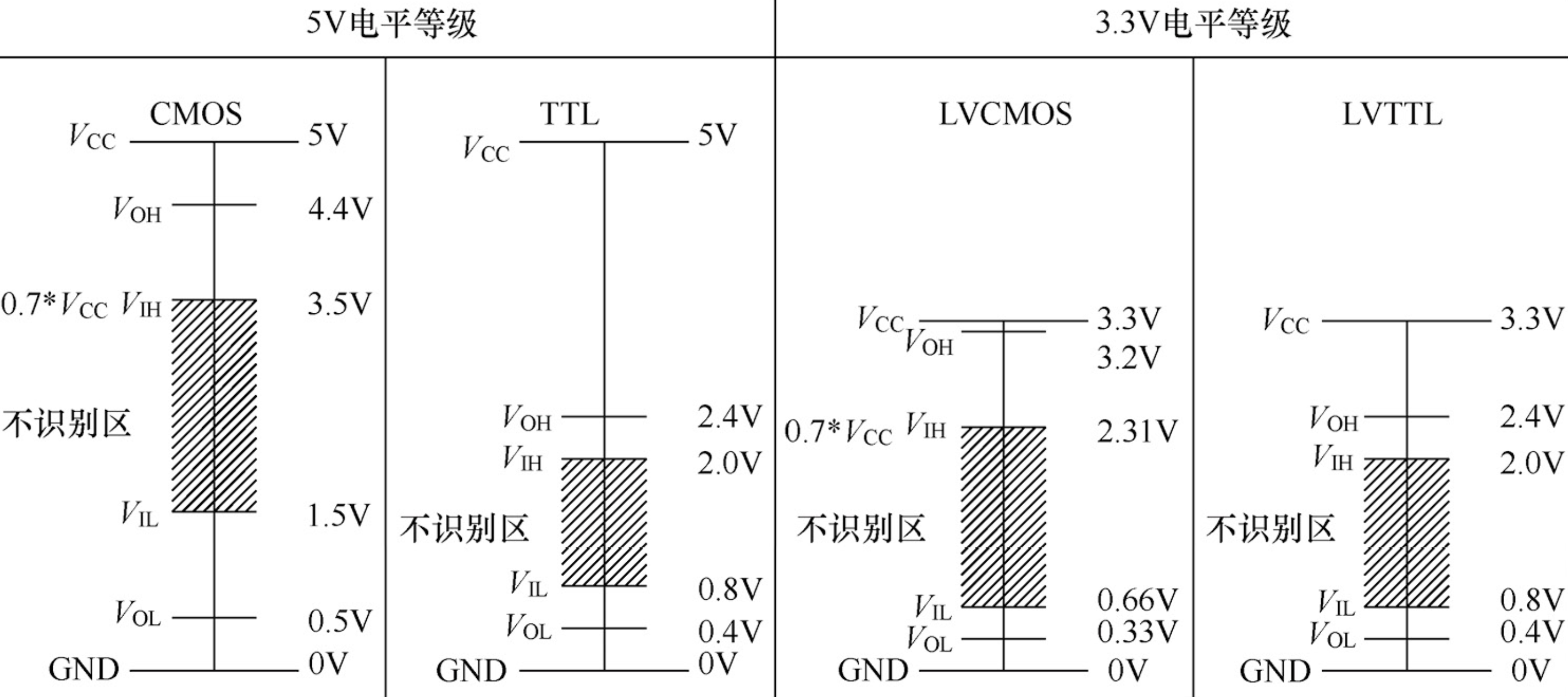

不同电平等级的逻辑器件之间相互传输信号时, 信号电压范围需要匹配

图中阴影区域的电平值就是不能被逻辑器件识别的电平值, 在这个区域既不是高电平, 也不是低电平. 很多设备失控, 都是因为电平值停留在了阴影区域(引脚处于浮空状态)

TTL 器件 和 CMOS 器件差异

TTL(晶体管-晶体管逻辑)和 CMOS(互补金属氧化物半导体)是两种不同类型的数字逻辑电路技术

| 特性 | TTL | CMOS |

|---|---|---|

| 工作原理 | 双极型晶体管(BJT) | 互补MOSFET(n型和p型) |

| 功耗 | 静态功耗较高,开关时有功耗 | 静态功耗极低,主要在开关时有功耗 |

| 速度 | 开关速度较快 | 现代CMOS速度高 |

| 电压范围 | 通常为5V(也有3.3V版本) | 从3V到15V不等,电压范围较宽 |

| 抗干扰性 | 抗干扰能力较弱,电源波动敏感 | 抗干扰能力较强,对电源波动和噪声更鲁棒 |

| 集成度 | 集成度较低,需要更多芯片面积 | 高集成度,同面积上集成更多功能 |

| 成本 | 生产成本较高 | 生产成本较低,尤其在大规模集成电路中表现显著 |

RS485 总线

现场总线定义了硬件接口和通信协议的标准. RS485在工业上的用途非常广泛

物理层

物理层规定了信号编码和传输方式, 传输介质, 接口信号的电气速率等

数据链路层

数据链路层分为介质访问控制(MAC)层, 逻辑链路控制层(LLC)

MAC层: 对传输信号进行发送和接收控制, 协议主要包含三种:

- 集中轮询协议: 主站周期性的轮询各节点

- 令牌总线协议: 多主站之间可以基于令牌传送协议工作, 持有令牌的总线可以轮询各节点

- 随机介入协议: 类似于多机系统中的并行总线管理机制

LLC层: 保证数据传输的指令设备上

应用层

应用层用于控制现场设备数据的传送和总线变量的访问, 定义了用户接口如何读写操作设备的信息和命令, 定义了信息, 请求的格式和内容

用户层

定义了现场设备读写信息和向网络其他设备分派信息的方法

RS485 没有规定软件协议格式, 可以由使用者自行定义软件协议

现场总线协议

| 总线类型 | 传输介质 | 传输速度 | 拓扑结构 | 应用领域 |

|---|---|---|---|---|

| Profibus | 双绞线 | 9.6 kbps - 12 Mbps | 总线、星形 | 工业自动化,过程控制 |

| Foundation Fieldbus | 双绞线 | 31.25 kbps | 总线、环形 | 过程控制 |

| Modbus | 双绞线、RS-485 | 9600 bps - 115.2 kbps | 总线、星形 | 工业设备数据交换 |

| CANopen | CAN总线 | 1 Mbps | 总线、星形 | 控制系统、运动控制 |

| DeviceNet | CAN总线 | 125 kbps - 500 kbps | 总线 | 自动化设备 |

| AS-Interface (AS-i) | 双绞线 | 166 kbps | 总线 | 传感器和执行器的连接 |

| HART | 电流环路 | 1200 bps | 点对点 | 过程控制,设备通讯 |

| Sercos | 光纤、双绞线 | 2 Mbps - 100 Mbps | 环形、星形 | 实时控制、伺服驱动 |

| EtherCAT | 双绞线、光纤 | 100 Mbps | 总线、星形 | 高性能实时控制 |

| Ethernet/IP | 双绞线、光纤 | 10/100/1000 Mbps | 星形 | 工业以太网,自动化系统 |

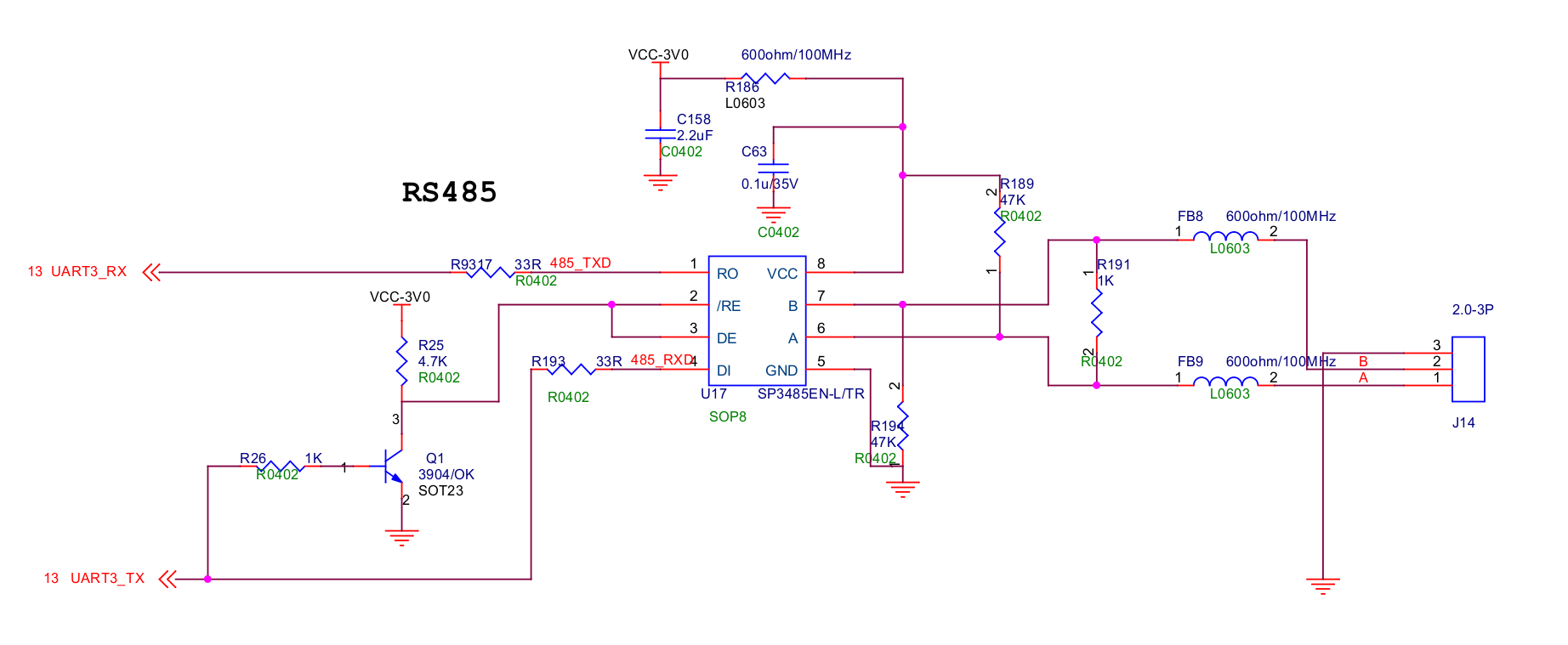

RS485 总线

主控芯片通过串口控制器将数据经过485芯片, 变为电气信号传输到485A 和 485B 两根信号线.

- 485总线是差分信号, 支持一主多从传输

- 使用特性阻抗为120欧的双绞线作为传输介质时的传输距离可达1200m

- 最大传输速度为10Mbps, 但是实际上和485芯片厂家有关系

- 同一时刻总线上只能有一个主机发送数据, 多个从机接收数据

- A B 之间的电压差要大于200mV为有效是逻辑1, 小于-200mV为逻辑0

- RS485 芯片的输入阻抗越大, 可以挂载的设备数量越多

| 数据传输速率 | 参考传输距离 | 说明 |

|---|---|---|

| 9600 bps | 1200 米 | 较低数据传输速率,信号衰减较小,传输距离较长 |

| 38400 bps | 1000 米 | 中等数据传输速率,距离适中 |

| 10000 kbps | 100 米 | 高速数据传输,信号衰减显著,传输距离较短 |

特性阻抗

电缆的特性阻抗(Characteristic Impedance)是描述电缆传输线特性的一项重要参数。它定义了电缆在高频信号下的电阻特性,与电缆的物理构造和材料有关

特性阻抗是指电缆或传输线在高频信号(交流信号)条件下的电阻值,它决定了信号沿电缆传输时的电流与电压之间的关系。特性阻抗是一个复数,通常用Z₀表示,其值为电缆传输线的实际阻抗,不随电缆长度变化。

常见485芯片对比

| 芯片型号 | 电源电压 | 传输速率 | 工作温度范围 | 驱动能力 | 接收灵敏度 |

|---|---|---|---|---|---|

| SP3485 | 3.3V 或 5V | 高达 10 Mbps | -40°C 到 +85°C | ±250 mA | -200 mV |

| MAX485 | 5V | 高达 2.5 Mbps | -40°C 到 +85°C | ±150 mA | -200 mV |

| SN75176 | 5V | 高达 1 Mbps | -40°C 到 +85°C | ±50 mA | -200 mV |

| ADM485 | 5V | 高达 2.5 Mbps | -40°C 到 +85°C | ±250 mA | -200 mV |

| LT1785 | 5V | 高达 10 Mbps | -40°C 到 +85°C | ±500 mA | -200 mV |

案例

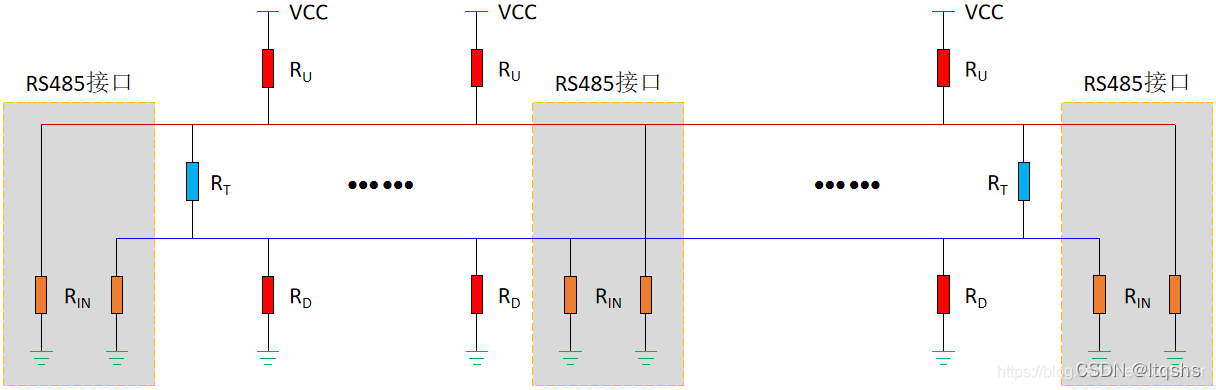

上图中 终端电阻 1K, 上下拉电阻47K

实际使用中上下拉电阻的选择要复杂的多,因为它不但与所采用的收发器有关,还与总线上的节点数量有关。收发器的输入阻抗也决定了总线所能挂载节点的数量.

RS485 特性

RS485标准TIA/EIA-485描述其支持32个单元负载, 通常认为12kΩ(输入阻抗)是一个单元负载, 理论上可以在总线上连接同一个厂家同型号RS485芯片的设备数量为32个.

12kΩ / 32 = 375Ω, 即RS485总线的等效负载必须大于等于375Ω

随着RS485的应用规模增大, 一条RS485总线上挂载32个设备不能再满足需求, 所以芯片制造商设计了输入阻抗为48KΩ(阻抗越大, 输入电流越小, 总线上可以挂载的节点越多), 这样可以挂载的设备数量增加到128个.

RS485波形数据关系

在RS485总线中, 当发送一个数据电平时, 485A 与 485B 信号线上将产生极性相反的电平.

电气信号规定: Va - Vb > 200mV = 1, Va - Vb < -200mV = 0

MCU内部UART控制器数量不够时, 可以选择两个普通I/O口模拟, 需要驱动程序支持

带屏蔽电缆: 有效隔离外部干扰, 同时减少电缆对外界的干扰, 屏蔽层需要接入大地(地球)

电缆阻抗和信号完整性

RS485 总线特性阻抗为120欧的起源

RS485 双绞线的优选线径是: 0.643mm

以太网线特性阻抗100欧的规定

同轴电缆特性阻抗50欧/75欧的规定

信号完整性

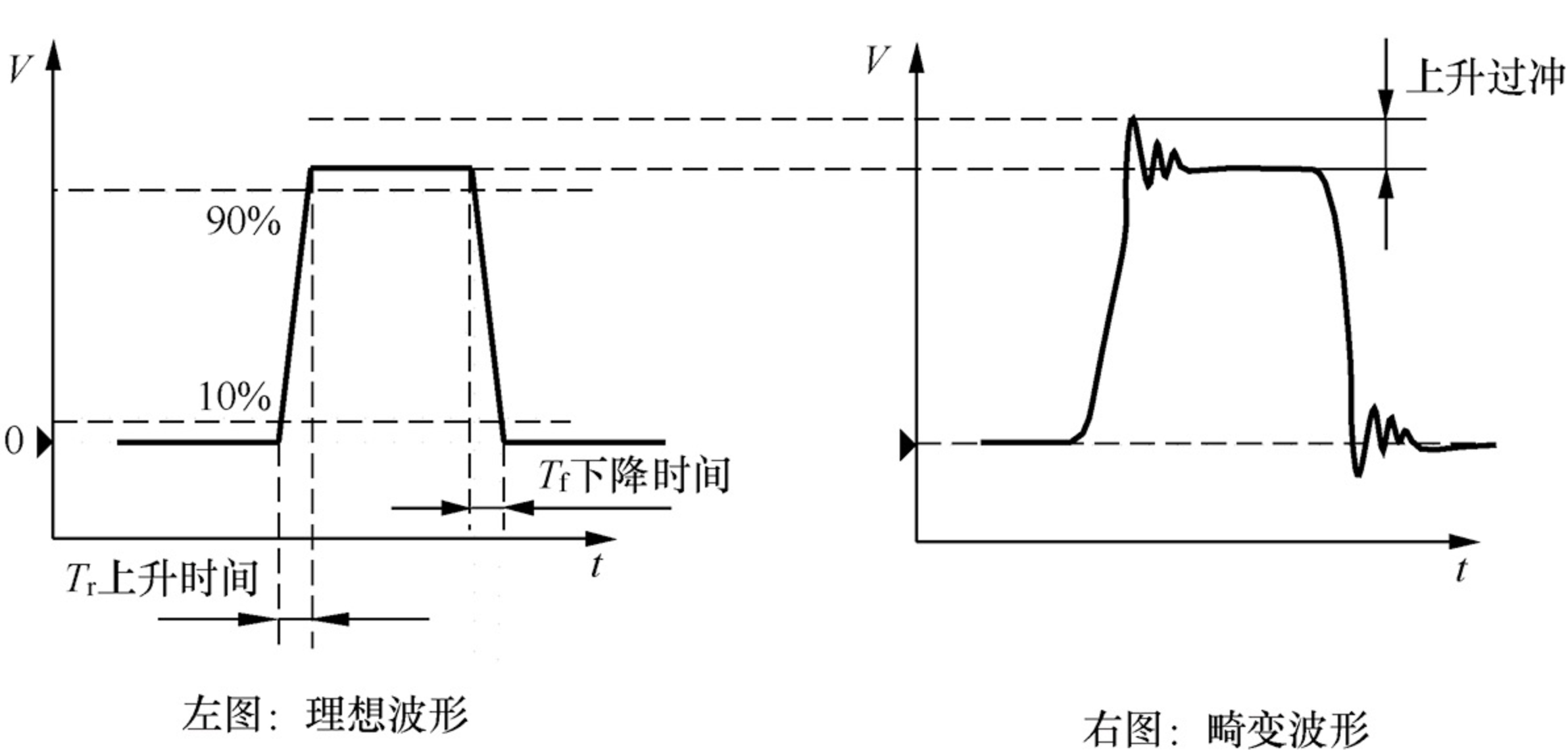

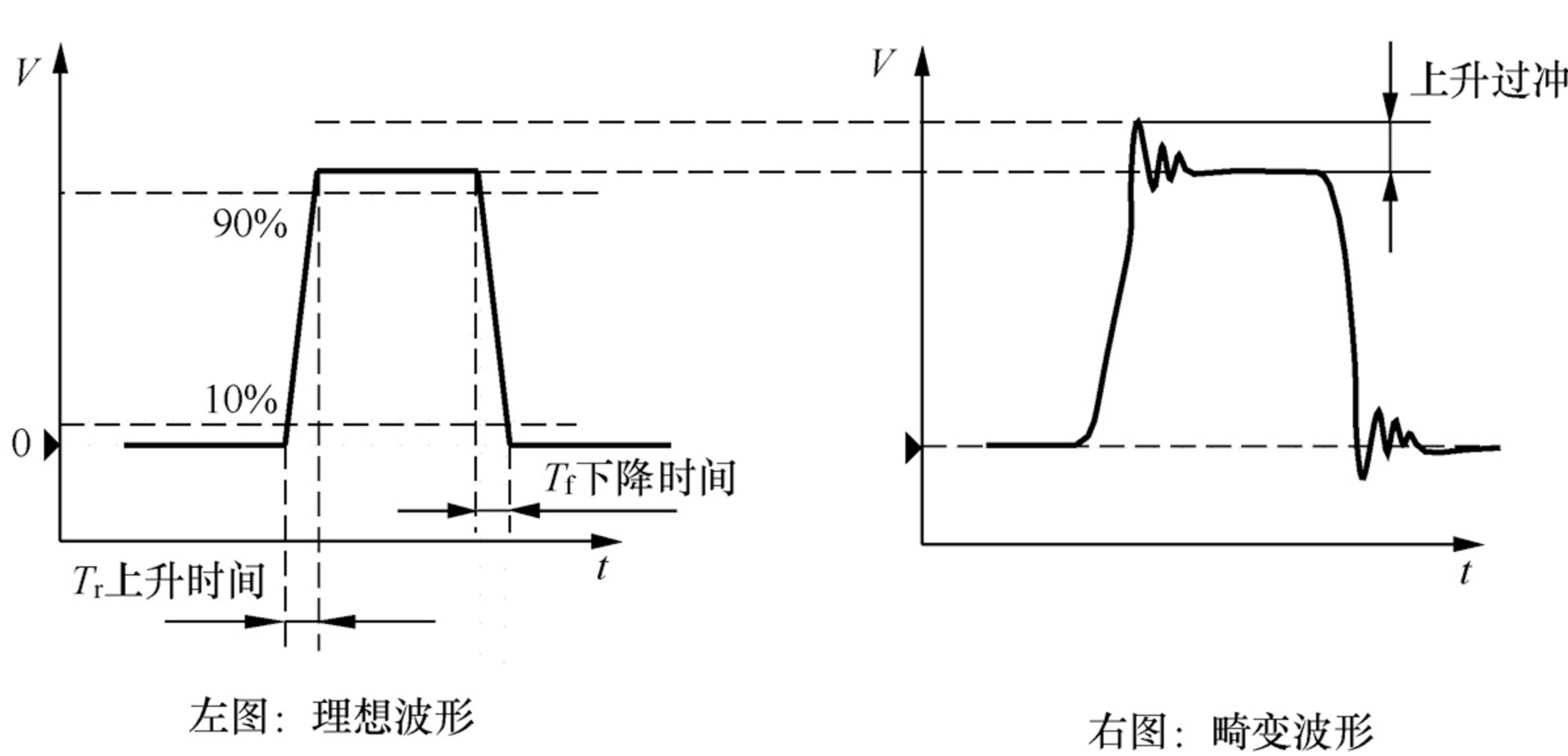

典型波形畸变

理想状态下, 数字信号的波形接近方波, 实际上, 信号会在干扰后产生畸变

MCU 的 I/O 阻抗是有一定标准的, 而PCB工程师在设计PCB走线时, 往往其阻抗比芯片管脚的输出阻抗要高, 因此会导致如下图信号波形畸变

-

过冲: 信号的波形高出高电平和低于低电平的部分. 芯片IC对过冲的高度和宽度有一定的容忍度, 过冲会让芯片内部的ESD防护二极管导通, 通常电流在100mA左右, 信号长期过冲会缩短芯片使用寿命,例如有的设计师错误的将5V的CAN芯片和3.3V的CPU直接通信

-

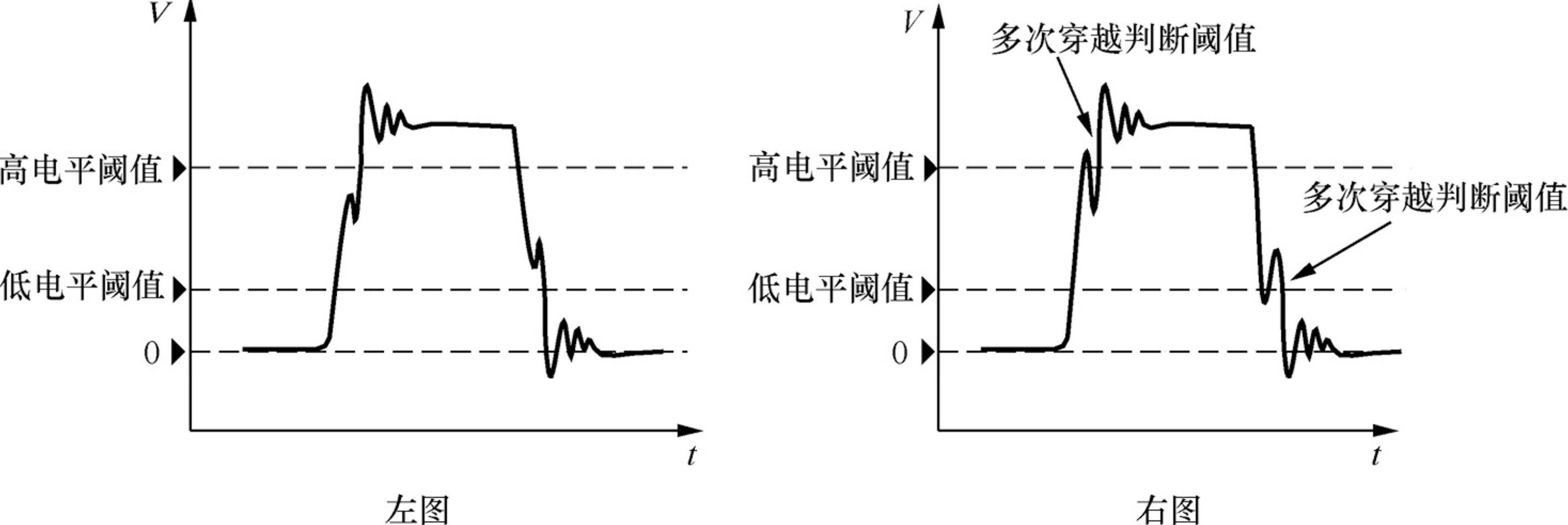

振铃: 信号高低电平存在上下震荡的情况, 可能导致信号识别错误

-

非单调性: 信号的上升沿或者下降沿出现回沟, 如下图

电子硬件工程师的技能和企业可提供的测试设备密切相关

随着智能设备的信号频率越来越高,集成IC功能越来越复杂,电子硬件工程师需要的更强大的开发辅助工具也越来越精密、昂贵。 许多企业暂时无法购置精密的测试设备,以致于电子硬件工程师的研发能力被限制,他们只能借助低频率示波器、万用表、电烙铁进行电子电路的设计与开发

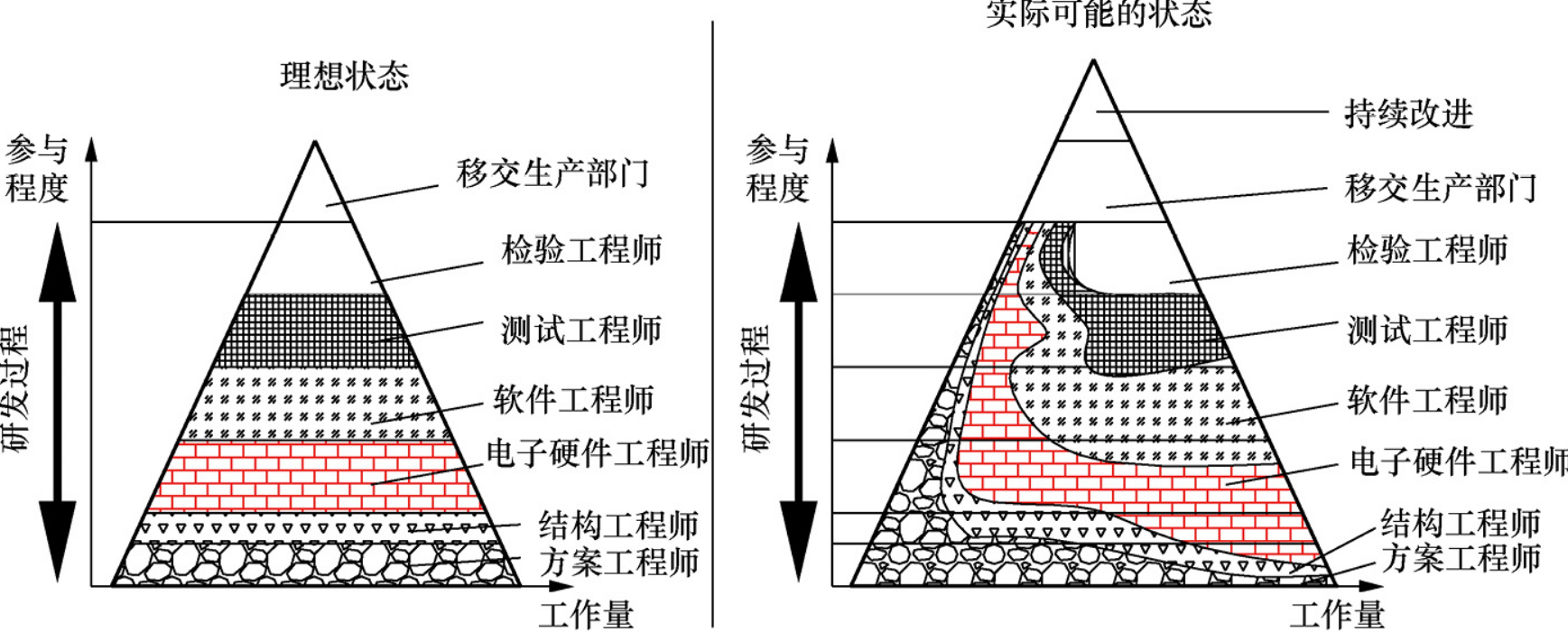

硬件研发与应用企业对信号完整性大致有以下3种态度。

- 不关心信号完整性,只要设备能通信,就开始批量生产,设备出了问题再来分析原因,重新设计PCB。

- 适当关心信号完整性,在设计电路、PCB时,凭借学识、经验控制阻抗、等长等基本要素;只要设备功能正常,通过高低温、静电、浪涌、脉冲群等测试,就开始批量生产,设备出了问题再分析具体原因。

- 关心信号完整性、电源完整性,按照“可预测、可设计、可验证、可复用、可传承”的要求设计产品。

信号反射对波形的影响

阻抗及时序匹配技术

RS485 通信故障及理论指导

案例一: RS485上拉电阻值,下拉电阻的影响

RS485 总线硬件电路驱动能力不足, 导致Va -Vb <= 200mV, 因此降低上下拉电阻的阻值, 提高驱动能力

匹配的终端电阻阻值不一定是120Ω,因为使用终端电阻是为了减少电缆的反射信号,其阻值与电缆的特性阻抗有关,通常在电缆特性阻抗额定值±20%的范围波动。例如,当电缆的特性阻抗为100Ω时,匹配的终端电阻值范围是80~120Ω

案例二: 电缆的直流电阻影响通信距离

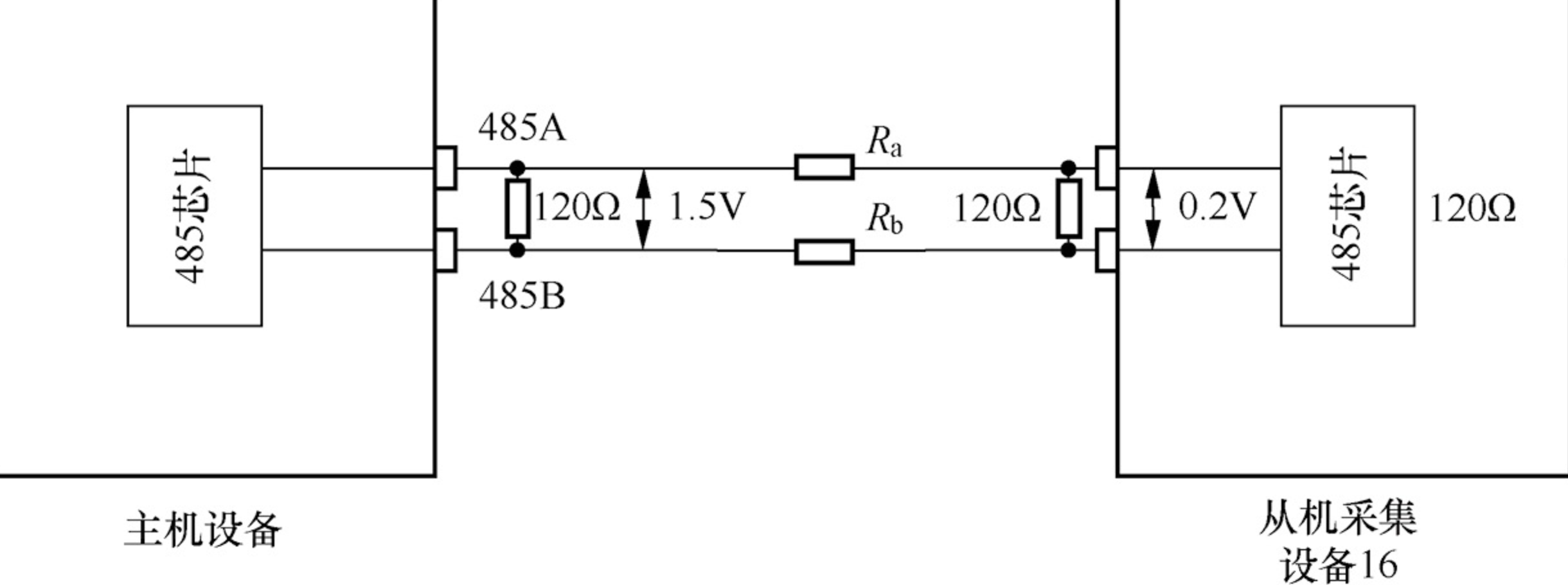

由于RS485的电气标准TIA/EIA-485-A规定RS485芯片输出端有数据逻辑高电平时驱动电压差Va−Vb>1.5V,电缆的直流电阻过大, 导致接收端电平识别的接收电压差Va−Vb<0.2V,如下图:

双绞线的直流电阻值应该小于 390 欧

案例三: 屏蔽层不可靠接地导致通信被干扰

强电电缆磁场耦合影响弱电信号