A133 WIFI 无法打开问题

报错日志

[ 5.778834] [ T193] sunxi-rfkill soc@2900000:rfkill: module version: v1.1.0

[ 5.786803] [ T193] sunxi-rfkill soc@2900000:rfkill: pinctrl_lookup_state(default) failed! return ffffffffffffffed

[ 5.798631] [ T193] sunxi-rfkill soc@2900000:rfkill: get gpio chip_en failed

[ 5.806645] [ T193] sunxi-rfkill soc@2900000:rfkill: power_en gpio=361 assert=1

[ 5.814973] [ T193] sunxi-rfkill soc@2900000:rfkill: wlan_busnum (1)

[ 5.822634] [ T193] sunxi-rfkill soc@2900000:rfkill: wlan power[0] (axp803-dldo1) voltage: 1800mV

[ 5.832704] [ T193] sunxi-rfkill soc@2900000:rfkill: wlan_regon gpio=359 assert=1

[ 5.841227] [ T193] sunxi-rfkill soc@2900000:rfkill: wlan_hostwake gpio=360 assert=1

[ 5.850019] [ T193] sunxi-rfkill soc@2900000:rfkill: wakeup source is enabled

[ 5.858251] [ T193] sunxi-rfkill soc@2900000:rfkill: bt power[0] (axp803-dldo1) voltage: 1800mV

[ 5.873840] [ T193] sunxi-rfkill soc@2900000:rfkill: bt_rst gpio=354 assert=0

[ 5.881922] [ T193] sun50iw10p1-r-pinctrl-aw 7022000.pinctrl: pin PL2 already requested by 7080000.uart; cannot claim for 7022000.pinctrl:354

[ 5.896201] [ T193] sun50iw10p1-r-pinctrl-aw 7022000.pinctrl: pin-354 (7022000.pinctrl:354) status -22

[ 5.906664] [ T193] sunxi-rfkill soc@2900000:rfkill: can't request bt_rst gpio 354

问题原因

PL2 引脚配置冲突

修改方案

/* bt session */

bt {

compatible = "allwinner,sunxi-bt";

clocks;

clock-names;

bt_power = "axp803-dldo1";

bt_power_vol = <1800000>;

bt_rst_n = <&r_pio PL 4 GPIO_ACTIVE_LOW>; // 修改PL2 为 PL4

};

RK3568 MIPI 屏幕无法点亮问题

报错日志

[ 5.685860] rockchip-vop2 fe040000.vop: [drm:vop2_bind] vp0 assign plane mask: 0x22, primary plane phy id: 5

[ 5.685891] rockchip-vop2 fe040000.vop: [drm:vop2_bind] vp1 assign plane mask: 0x15, primary plane phy id: 4

[ 5.685899] rockchip-vop2 fe040000.vop: [drm:vop2_bind] vp2 assign plane mask: 0x8, primary plane phy id: 3

[ 5.686322] [drm] failed to init overlay plane Cluster0-win1

[ 5.686358] [drm] failed to init overlay plane Cluster1-win1

[ 5.686503] rockchip-drm display-subsystem: bound fe040000.vop (ops 0xffffffc0096e8f78)

[ 5.690316] rockchip-drm display-subsystem: bound fe0a0000.hdmi (ops 0xffffffc0096f7b08)

[ 5.690492] rockchip-drm display-subsystem: bound fe070000.dsi (ops 0xffffffc0096f9460)

[ 5.734417] rockchip-vop2 fe040000.vop: [drm:vop2_isr] *ERROR* POST_BUF_EMPTY irq err at vp1

[ 5.818653] rockchip-drm display-subsystem: [drm] fb0: rockchipdrmfb frame buffer device

查看当前的显示状态

root@ubuntu2004:~# cat /sys/kernel/debug/dri/0/summary

Video Port0: ACTIVE

Connector: HDMI-A-1

bus_format[2025]: YUV8_1X24

overlay_mode[1] output_mode[f] color_space[3], eotf:0

Display mode: 1024x768p60

clk[65000] real_clk[65000] type[48] flag[a]

H: 1024 1048 1184 1344

V: 768 771 777 806

Smart1-win0: ACTIVE

win_id: 1

format: XR24 little-endian (0x34325258) SDR[0] color_space[0] glb_alpha[0xff]

rotate: xmirror: 0 ymirror: 0 rotate_90: 0 rotate_270: 0

csc: y2r[0] r2y[1] csc mode[1]

zpos: 0

src: pos[0, 0] rect[1024 x 768]

dst: pos[0, 0] rect[1024 x 768]

buf[0]: addr: 0x000000007eda8000 pitch: 4096 offset: 0

Video Port1: ACTIVE

Connector: DSI-1

bus_format[100a]: RGB888_1X24

overlay_mode[0] output_mode[0] color_space[0], eotf:0

Display mode: 800x1280p50

clk[60000] real_clk[60000] type[48] flag[a]

H: 800 872 896 920

V: 1280 1292 1294 1304

Smart0-win0: ACTIVE

win_id: 0

format: XR24 little-endian (0x34325258) SDR[0] color_space[0] glb_alpha[0xff]

rotate: xmirror: 0 ymirror: 0 rotate_90: 0 rotate_270: 0

csc: y2r[0] r2y[0] csc mode[0]

zpos: 1

src: pos[0, 0] rect[800 x 1280]

dst: pos[0, 0] rect[800 x 1280]

buf[0]: addr: 0x000000007f0a8000 pitch: 3200 offset: 0

Video Port2: DISABLED

原因分析

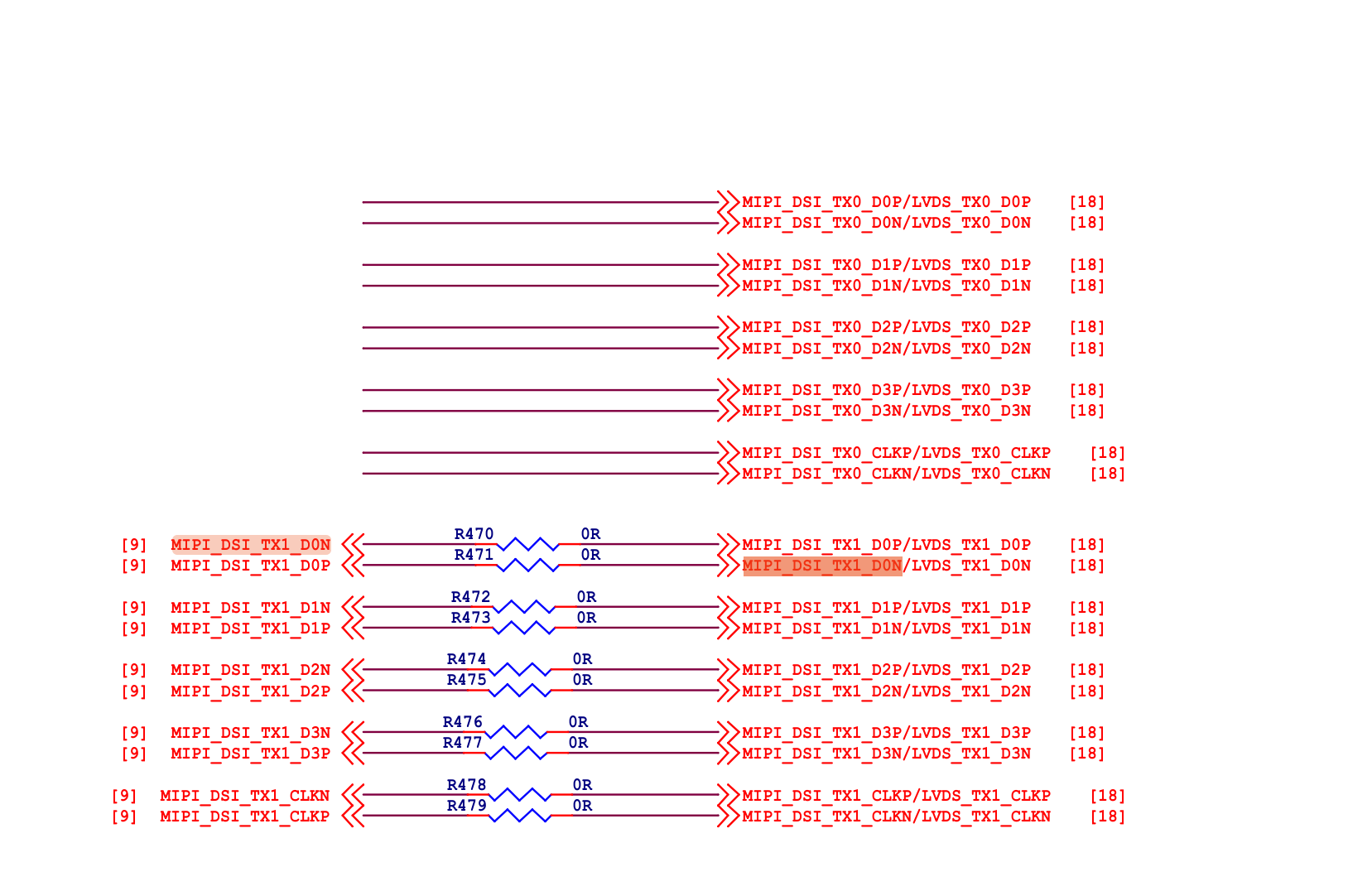

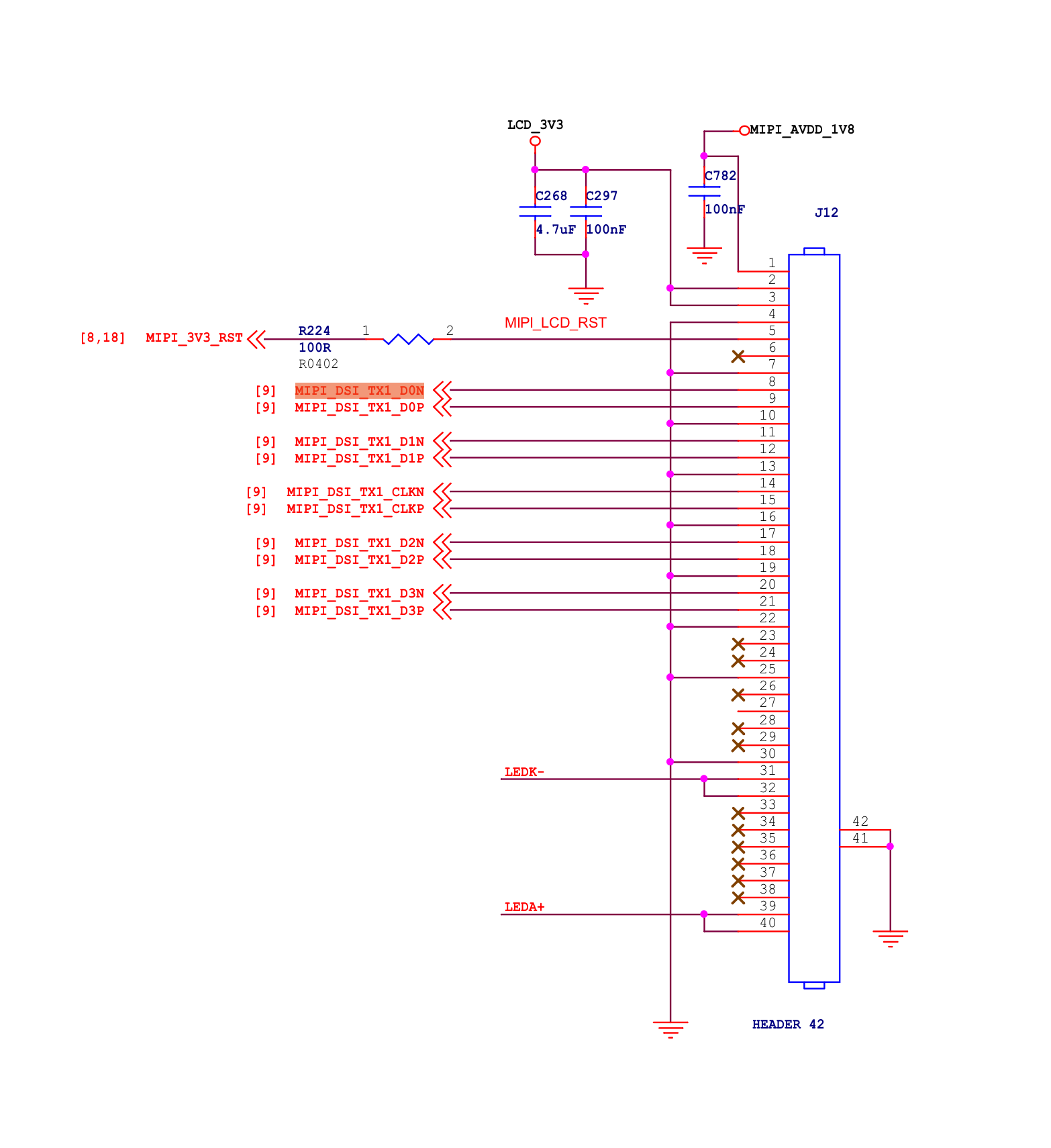

为什么要加 *-lane-pol-swap?

硬件布线不同:如果你硬件设计时 MIPI 差分对(比如 D0P/D0N)接反了,导致物理上的信号正负颠倒,就需要通过软件配置极性翻转,让信号逻辑方向正确。

解决方案

//video_phy0 是第一个(一般给主屏),video_phy1 是第二个(副屏)

&video_phy1 {

status = "okay";

clock-lane-pol-swap; // 时钟通道(Clock Lane)的极性反转,即将 MIPI 时钟通道的差分信号正负互换

data0-lane-pol-swap;

data1-lane-pol-swap;

data2-lane-pol-swap;

data3-lane-pol-swap;

};

0

次点赞