概念

Clock 时钟就是 SoC 中的脉搏,由它来控制各个部件按各自的节奏跳动。比如,CPU主频设置,串口的波特率设置,I2S的采样率设置,I2C的速率设置等等。这些不同的clock设置,都需要从某个或某几个时钟源头而来,最终开枝散叶,形成一颗时钟树。可通过 cat /sys/kernel/debug/clk/clk_summary 查看这棵时钟树。

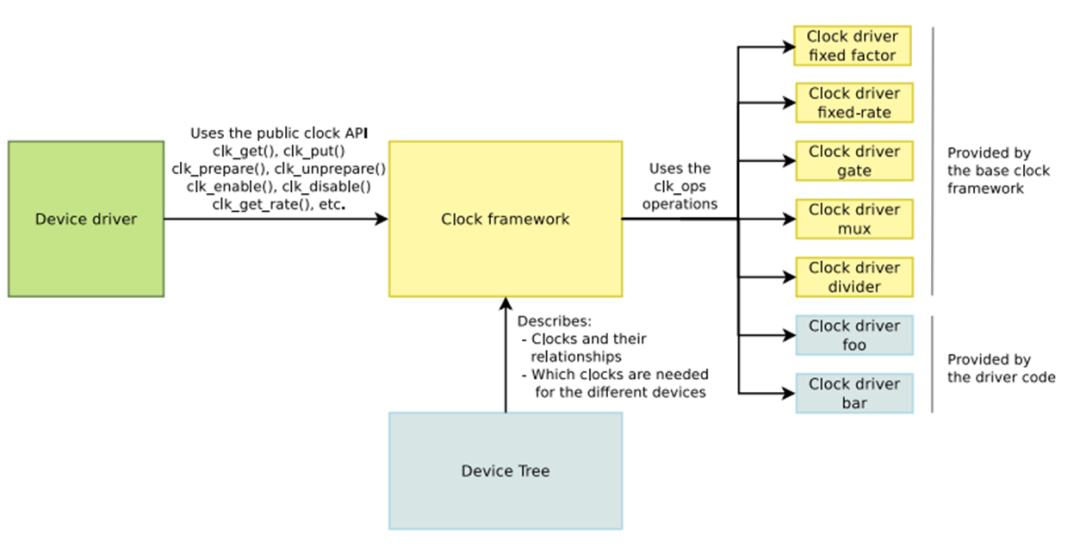

框架

内核中用 CCF 框架来管理 clock,如下所示,右边是 clock 提供者,即 Clock Provider;中间是 CCF;左边是设备驱动的 clock 使用者,即 Clock Consumer

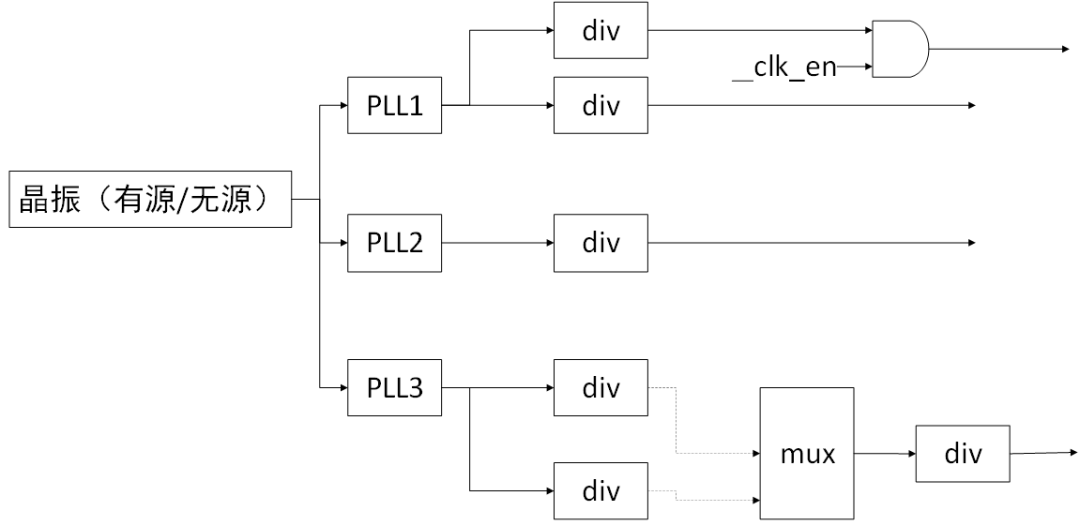

时钟树

CLOCK 相关的器件包括:

- 用于产生 CLOCK 的 Oscillator(有源振荡器,也称作谐振荡器)或者Crystal(无源振荡器,也称晶振);

- 用于倍频的 PLL(锁相环,Phase Locked Loop);

- 用于分频的Divider;

- 用于多路选择的 MUX;

- 用于CLOCK ENABLE控制的与门;

- 使用 CLOCK 的硬件模块(可称作CONSUMER);

- 根节点一般是 Oscillator(有源振荡器)或者 Crystal(无源振荡器)。

- 中间节点有很多种,包括 PLL(锁相环,用于提升频率的),Divider(分频器,用于降频的),Mux(从多个clock path中选择一个),Gate(用来控制ON/OFF的)。

- 叶节点是使用 clock 做为输入的、有具体功能的 HW block。

DTS

rk3399.dtsi

pmucru: pmu-clock-controller@ff750000 {

compatible = "rockchip,rk3399-pmucru";

reg = <0x0 0xff750000 0x0 0x1000>;

#clock-cells = <1>;

#reset-cells = <1>;

assigned-clocks = <&pmucru PLL_PPLL>, <&pmucru FCLK_CM0S_SRC_PMU>;

assigned-clock-rates = <676000000>, <97000000>;

};

cru: clock-controller@ff760000 {

compatible = "rockchip,rk3399-cru";

reg = <0x0 0xff760000 0x0 0x1000>;

#clock-cells = <1>;

#reset-cells = <1>;

assigned-clocks =

<&cru ACLK_VOP0>, <&cru HCLK_VOP0>,

<&cru ACLK_VOP1>, <&cru HCLK_VOP1>,

<&cru ARMCLKL>, <&cru ARMCLKB>,

<&cru PLL_GPLL>, <&cru PLL_CPLL>,

<&cru ACLK_GPU>, <&cru PLL_NPLL>,

<&cru ACLK_PERIHP>, <&cru HCLK_PERIHP>,

<&cru PCLK_PERIHP>,

<&cru ACLK_PERILP0>, <&cru HCLK_PERILP0>,

<&cru PCLK_PERILP0>, <&cru ACLK_CCI>,

<&cru HCLK_PERILP1>, <&cru PCLK_PERILP1>,

<&cru ACLK_VIO>, <&cru ACLK_HDCP>,

<&cru ACLK_GIC_PRE>,

<&cru PCLK_DDR>;

assigned-clock-rates =

<400000000>, <200000000>,

<400000000>, <200000000>,

<816000000>, <816000000>,

<594000000>, <800000000>,

<200000000>, <1000000000>,

<150000000>, <75000000>,

<37500000>,

<100000000>, <100000000>,

<50000000>, <600000000>,

<100000000>, <50000000>,

<400000000>, <400000000>,

<200000000>,

<200000000>;

};

i2s0: i2s@ff880000 {

compatible = "rockchip,rk3399-i2s", "rockchip,rk3066-i2s";

reg = <0x0 0xff880000 0x0 0x1000>;

rockchip,grf = <&grf>;

interrupts = <GIC_SPI 39 IRQ_TYPE_LEVEL_HIGH 0>;

dmas = <&dmac_bus 0>, <&dmac_bus 1>;

dma-names = "tx", "rx";

clock-names = "i2s_clk", "i2s_hclk";

clocks = <&cru SCLK_I2S0_8CH>, <&cru HCLK_I2S0_8CH>;

resets = <&cru SRST_I2S0_8CH>, <&cru SRST_H_I2S0_8CH>;

reset-names = "reset-m", "reset-h";

pinctrl-names = "default";

pinctrl-0 = <&i2s0_8ch_bus>;

power-domains = <&power RK3399_PD_SDIOAUDIO>;

#sound-dai-cells = <0>;

status = "disabled";

};

pinctrl: pinctrl {

compatible = "rockchip,rk3399-pinctrl";

rockchip,grf = <&grf>;

rockchip,pmu = <&pmugrf>;

#address-cells = <2>;

#size-cells = <2>;

ranges;

i2s0 {

i2s0_2ch_bus: i2s0-2ch-bus {

rockchip,pins =

<3 RK_PD0 1 &pcfg_pull_none>,

<3 RK_PD1 1 &pcfg_pull_none>,

<3 RK_PD2 1 &pcfg_pull_none>,

<3 RK_PD3 1 &pcfg_pull_none>,

<3 RK_PD7 1 &pcfg_pull_none>,

<4 RK_PA0 1 &pcfg_pull_none>;

};

i2s0_8ch_bus: i2s0-8ch-bus {

rockchip,pins =

<3 RK_PD0 1 &pcfg_pull_none>,

<3 RK_PD1 1 &pcfg_pull_none>,

<3 RK_PD2 1 &pcfg_pull_none>,

<3 RK_PD3 1 &pcfg_pull_none>,

<3 RK_PD4 1 &pcfg_pull_none>,

<3 RK_PD5 1 &pcfg_pull_none>,

<3 RK_PD6 1 &pcfg_pull_none>,

<3 RK_PD7 1 &pcfg_pull_none>;

};

i2s_8ch_mclk: i2s-8ch-mclk {

rockchip,pins = <4 RK_PA0 1 &pcfg_pull_none>;

};

};

}

rk3399-evb.dtsi

es8316: es8316@10 {

status = "okay";

#sound-dai-cells = <0>;

compatible = "everest,es8316";

reg = <0x10>;

clocks = <&cru SCLK_I2S_8CH_OUT>;

clock-names = "mclk";

pinctrl-names = "default";

pinctrl-0 = <&i2s_8ch_mclk>;

spk-con-gpio = <&gpio4 4 GPIO_ACTIVE_HIGH>;

//hp-det-gpio = <&gpio4 28 GPIO_ACTIVE_LOW>;

};

RK3399 Linux 4.19

enable prepare protect duty

clock count count count rate accuracy phase cycle

---------------------------------------------------------------------------------------------

rk808-clkout2 2 2 0 32768 0 0 50000

rk808-clkout1 0 0 0 32768 0 0 50000

xin32k 0 0 0 32768 0 0 50000

clkin_gmac 1 1 0 125000000 0 0 50000

clk_rmii_src 1 4 0 125000000 0 0 50000

clk_rmii_tx 1 2 0 125000000 0 0 50000

clk_rmii_rx 0 1 0 125000000 0 0 50000

clk_mac_ref 0 1 0 125000000 0 0 50000

clk_mac_refout 0 1 0 125000000 0 0 50000

dummy_vpll 0 0 0 0 0 0 50000

dummy_cpll 0 0 0 0 0 0 50000

clk_test_pre 0 0 0 0 0 0 50000

clk_test 0 0 0 0 0 0 50000

clk_test_frac 0 0 0 0 0 0 50000

clk_cifout_src 0 0 0 0 0 0 50000

clk_testout2_pll_src 0 0 0 0 0 0 50000

clk_testout1_pll_src 0 0 0 0 0 0 50000

clk_uart_src 0 0 0 0 0 0 50000

clk_uart3_div 0 0 0 0 0 0 50000

clk_uart3_frac 0 0 0 0 0 0 50000

clk_uart2_div 0 0 0 0 0 0 50000

clk_uart2_frac 0 0 0 0 0 0 50000

clk_uart1_div 0 0 0 0 0 0 50000

clk_uart1_frac 0 0 0 0 0 0 50000

clk_i2s1_div 0 0 0 0 0 0 50000

clk_i2s1_frac 0 0 0 0 0 0 50000

clk_spdif_rec_dptx 0 0 0 0 0 0 50000

clk_spdif_div 0 0 0 0 0 0 50000

clk_spdif_frac 0 0 0 0 0 0 50000

xin24m 21 21 0 24000000 0 0 50000

clk_timer11 0 0 0 24000000 0 0 50000

clk_timer10 0 0 0 24000000 0 0 50000

clk_timer09 0 0 0 24000000 0 0 50000

clk_timer08 0 0 0 24000000 0 0 50000

clk_timer07 0 0 0 24000000 0 0 50000

clk_timer06 0 0 0 24000000 0 0 50000

clk_timer05 0 0 0 24000000 0 0 50000

clk_timer04 0 0 0 24000000 0 0 50000

clk_timer03 0 0 0 24000000 0 0 50000

clk_timer02 0 0 0 24000000 0 0 50000

clk_timer01 0 0 0 24000000 0 0 50000

clk_timer00 1 1 0 24000000 0 0 50000

clk_test_24m 0 0 0 24000000 0 0 50000

clk_mipidphy_cfg 0 0 0 24000000 0 0 50000

clk_dphy_rx0_cfg 0 0 0 24000000 0 0 50000

clk_dphy_tx1rx1_cfg 0 0 0 24000000 0 0 50000

clk_dphy_tx0_cfg 0 0 0 24000000 0 0 50000

clk_mipidphy_ref 0 0 0 24000000 0 0 50000

clk_dphy_pll 0 0 0 24000000 0 0 50000

clk_cifout 0 0 0 6000000 0 0 50000

clk_hdmi_cec 1 2 0 32743 0 0 50000

clk_hdmi_sfr 1 2 0 24000000 0 0 50000

clk_testout2 0 0 0 750000 0 0 50000

clk_testout_2io 0 0 0 750000 0 0 50000

clk_testout1 0 0 0 750000 0 0 50000

clk_tsadc 1 1 0 750000 0 0 50000

clk_saradc 1 1 0 1000000 0 0 50000

clk_pciephy_ref 0 0 0 24000000 0 0 50000

clk_pcie_pm 0 0 0 24000000 0 0 50000

aclk_pvtm_gpu 0 0 0 24000000 0 0 50000

clk_dfimon1_timer 0 0 0 24000000 0 0 50000

clk_dfimon0_timer 0 0 0 24000000 0 0 50000

clk_pvtm_ddr 0 0 0 24000000 0 0 50000

clk_uart3 0 0 0 24000000 0 0 50000

clk_uart2 1 1 0 24000000 0 0 50000

clk_uart1 0 0 0 24000000 0 0 50000

clk_uart0 0 0 0 24000000 0 0 50000

clk_pvtm_core_b 0 0 0 24000000 0 0 50000

clk_pvtm_core_l 0 0 0 24000000 0 0 50000

clk_uphy1_tcpdphy_ref 1 3 0 24000000 0 0 50000

clk_uphy0_tcpdphy_ref 1 3 0 24000000 0 0 50000

clk_usb3otg1_suspend 1 1 0 24000000 0 0 50000

clk_usb3otg0_suspend 1 1 0 24000000 0 0 50000

clk_usb3otg1_ref 1 1 0 24000000 0 0 50000

clk_usb3otg0_ref 1 1 0 24000000 0 0 50000

upll 1 1 0 24000000 0 0 50000

clk_sdmmc 1 5 0 800000 0 0 50000

sdmmc_sample 0 1 0 400000 0 0 50000

sdmmc_drv 0 1 0 400000 0 90 50000

clk_usb2phy1_ref 2 3 0 24000000 0 0 50000

clk_usbphy1_480m 4 6 0 480000000 0 0 50000

clk_usbphy1_480m_src 0 0 0 480000000 0 0 50000

clk_usb2phy0_ref 2 3 0 24000000 0 0 50000

clk_usbphy0_480m 4 6 0 480000000 0 0 50000

clk_usbphy0_480m_src 0 0 0 480000000 0 0 50000

clk_usbphy_480m 0 0 0 480000000 0 0 50000

clk_hsicphy 0 0 0 480000000 0 0 50000

pll_vpll 0 0 0 1188000000 0 0 50000

vpll 1 3 0 24000000 0 0 50000

dclk_vop1_div 0 2 0 6000000 0 0 50000

dclk_vop1 0 1 0 6000000 0 0 50000

dclk_vop1_frac 0 0 0 300000 0 0 50000

vpll_aclk_cci_src 0 0 0 24000000 0 0 50000

pll_npll 1 1 0 600000000 0 0 50000

npll 5 7 0 600000000 0 0 50000

aclk_vdu_pre 2 3 0 300000000 0 0 50000

aclk_vdu_noc 1 1 0 300000000 0 0 50000

aclk_vdu 0 4 0 300000000 0 0 50000

hclk_vdu_pre 1 2 0 150000000 0 0 50000

hclk_vdu_noc 1 1 0 150000000 0 0 50000

hclk_vdu 0 4 0 150000000 0 0 50000

aclk_usb3 4 5 0 300000000 0 0 50000

aclk_usb3_grf 2 2 0 300000000 0 0 50000

aclk_usb3_rksoc_axi_perf 0 0 0 300000000 0 0 50000

aclk_usb3otg1 1 1 0 300000000 0 0 50000

aclk_usb3otg0 1 1 0 300000000 0 0 50000

aclk_usb3_noc 1 1 0 300000000 0 0 50000

clk_vdu_core 0 1 0 300000000 0 0 50000

clk_vdu_ca 0 1 0 300000000 0 0 50000

clk_isp1 0 0 0 300000000 0 0 50000

clk_isp0 0 0 0 300000000 0 0 50000

clk_dp_core 0 0 0 120000000 0 0 50000

clk_pcie_core_cru 0 0 0 75000000 0 0 50000

clk_pciephy_ref100m 0 0 0 60000000 0 0 50000

npll_cs 1 1 0 600000000 0 0 50000

clk_cs 1 1 0 150000000 0 0 50000

clk_dbg_noc 1 1 0 150000000 0 0 50000

clk_dbg_cxcs 0 0 0 150000000 0 0 50000

npll_aclk_cci_src 1 1 0 600000000 0 0 50000

aclk_cci_pre 2 2 0 600000000 0 0 50000

aclk_cci_grf 0 0 0 600000000 0 0 50000

aclk_cci_noc1 1 1 0 600000000 0 0 50000

aclk_cci_noc0 1 1 0 600000000 0 0 50000

aclk_cci 0 0 0 600000000 0 0 50000

aclk_adb400m_pd_core_b 0 0 0 600000000 0 0 50000

aclk_adb400m_pd_core_l 0 0 0 600000000 0 0 50000

clk_gmac 1 2 0 30000000 0 0 50000

pll_gpll 1 1 0 800000000 0 0 50000

gpll 27 31 0 800000000 0 0 50000

aclk_gpu_pre 0 1 0 200000000 0 0 50000

aclk_gpu_grf 0 0 0 200000000 0 0 50000

aclk_perf_gpu 0 0 0 200000000 0 0 50000

aclk_gpu 0 3 0 200000000 0 0 50000

clk_i2s2_div 0 0 0 800000000 0 0 50000

clk_i2s2_frac 0 0 0 40000000 0 0 50000

clk_i2s0_div 0 0 0 800000000 0 0 50000

clk_i2s0_frac 0 0 0 40000000 0 0 50000

clk_sdio 1 4 0 200000000 0 0 50000

sdio_sample 0 1 0 100000000 0 144 50000

sdio_drv 0 1 0 100000000 0 90 50000

clk_uart0_src 0 0 0 800000000 0 0 50000

clk_uart0_div 0 0 0 800000000 0 0 50000

clk_uart0_frac 0 0 0 40000000 0 0 50000

aclk_vop1_pre 2 3 0 400000000 0 0 50000

aclk_vop1_noc 1 1 0 400000000 0 0 50000

aclk_vop1 0 4 0 400000000 0 0 50000

hclk_vop1_pre 1 2 0 100000000 0 0 50000

hclk_vop1_noc 1 1 0 100000000 0 0 50000

hclk_vop1 0 4 0 100000000 0 0 50000

aclk_vop0_pre 3 3 0 400000000 0 0 50000

aclk_vop0_noc 1 1 0 400000000 0 0 50000

aclk_vop0 1 5 0 400000000 0 0 50000

hclk_vop0_pre 2 2 0 100000000 0 0 50000

hclk_vop0_noc 1 1 0 100000000 0 0 50000

hclk_vop0 1 5 0 100000000 0 0 50000

pclk_ddr 1 1 0 200000000 0 0 50000

pclk_ddr_sgrf 0 0 0 200000000 0 0 50000

pclk_cic 0 0 0 200000000 0 0 50000

pclk_ddr_mon 0 0 0 200000000 0 0 50000

pclk_center_main_noc 1 1 0 200000000 0 0 50000

aclk_vcodec_pre 2 3 0 400000000 0 0 50000

aclk_vcodec_noc 1 1 0 400000000 0 0 50000

aclk_vcodec 0 5 0 400000000 0 0 50000

hclk_vcodec_pre 1 2 0 200000000 0 0 50000

hclk_vcodec_noc 1 1 0 200000000 0 0 50000

hclk_vcodec 0 5 0 200000000 0 0 50000

clk_rga_core 0 1 0 400000000 0 0 50000

aclk_rga_pre 2 3 0 400000000 0 0 50000

aclk_rga_noc 1 1 0 400000000 0 0 50000

aclk_rga 0 2 0 400000000 0 0 50000

hclk_rga_pre 1 2 0 200000000 0 0 50000

hclk_rga_noc 1 1 0 200000000 0 0 50000

hclk_rga 0 2 0 200000000 0 0 50000

aclk_iep_pre 2 3 0 400000000 0 0 50000

aclk_iep_noc 1 1 0 400000000 0 0 50000

aclk_iep 0 4 0 400000000 0 0 50000

hclk_iep_pre 1 2 0 200000000 0 0 50000

hclk_iep_noc 1 1 0 200000000 0 0 50000

hclk_iep 0 4 0 200000000 0 0 50000

aclk_vio 2 2 0 400000000 0 0 50000

aclk_vio_noc 2 2 0 400000000 0 0 50000

pclk_vio 1 1 0 200000000 0 0 50000

pclk_vio_grf 1 2 0 200000000 0 0 50000

pclk_mipi_dsi1 0 0 0 200000000 0 0 50000

pclk_mipi_dsi0 0 0 0 200000000 0 0 50000

aclk_hdcp 3 4 0 400000000 0 0 50000

aclk_hdcp22 0 0 0 400000000 0 0 50000

aclk_hdcp_noc 2 2 0 400000000 0 0 50000

pclk_hdcp 2 3 0 200000000 0 0 50000

pclk_gasket 0 0 0 200000000 0 0 50000

pclk_hdcp22 0 0 0 200000000 0 0 50000

pclk_dp_ctrl 0 0 0 200000000 0 0 50000

pclk_hdmi_ctrl 1 2 0 200000000 0 0 50000

pclk_hdcp_noc 2 2 0 200000000 0 0 50000

hclk_hdcp 1 2 0 200000000 0 0 50000

hclk_hdcp22 0 0 0 200000000 0 0 50000

hclk_hdcp_noc 2 2 0 200000000 0 0 50000

pclk_edp 2 2 0 100000000 0 0 50000

pclk_edp_ctrl 1 3 0 100000000 0 0 50000

pclk_edp_noc 1 1 0 100000000 0 0 50000

clk_vop1_pwm 0 0 0 100000000 0 0 50000

clk_vop0_pwm 0 0 0 100000000 0 0 50000

aclk_isp1 2 3 0 400000000 0 0 50000

aclk_isp1_wrapper 0 0 0 400000000 0 0 50000

aclk_isp1_noc 1 1 0 400000000 0 0 50000

hclk_isp1 1 2 0 200000000 0 0 50000

hclk_isp1_wrapper 0 0 0 200000000 0 0 50000

hclk_isp1_noc 1 1 0 200000000 0 0 50000

aclk_isp0 2 3 0 400000000 0 0 50000

aclk_isp0_wrapper 0 0 0 400000000 0 0 50000

aclk_isp0_noc 1 1 0 400000000 0 0 50000

hclk_isp0 1 2 0 200000000 0 0 50000

hclk_isp0_wrapper 0 0 0 200000000 0 0 50000

hclk_isp0_noc 1 1 0 200000000 0 0 50000

aclk_gic_pre 2 2 0 200000000 0 0 50000

aclk_gic_adb400_gic_2_core_b 0 0 0 200000000 0 0 50000

aclk_gic_adb400_gic_2_core_l 0 0 0 200000000 0 0 50000

aclk_gic_adb400_core_b_2_gic 0 0 0 200000000 0 0 50000

aclk_gic_adb400_core_l_2_gic 0 0 0 200000000 0 0 50000

aclk_gic_noc 2 2 0 200000000 0 0 50000

aclk_gic 1 1 0 200000000 0 0 50000

clk_spi5 0 0 0 50000000 0 0 50000

clk_spi4 0 0 0 50000000 0 0 50000

clk_spi2 0 0 0 50000000 0 0 50000

clk_spi0 0 0 0 50000000 0 0 50000

clk_ddrc_gpll_src 0 0 0 800000000 0 0 50000

clk_i2c7 0 0 0 100000000 0 0 50000

clk_i2c6 0 1 0 200000000 0 0 50000

clk_i2c5 0 0 0 100000000 0 0 50000

clk_i2c3 0 0 0 100000000 0 0 50000

clk_i2c2 0 0 0 100000000 0 0 50000

clk_i2c1 0 1 0 200000000 0 0 50000

clk_spi1 0 0 0 50000000 0 0 50000

pclk_alive 5 5 0 100000000 0 0 50000

pclk_sgrf 0 0 0 100000000 0 0 50000

pclk_pmu_intr_arb 0 0 0 100000000 0 0 50000

pclk_timer1 0 0 0 100000000 0 0 50000

pclk_timer0 1 1 0 100000000 0 0 50000

pclk_gpio4 1 1 0 100000000 0 0 50000

pclk_gpio3 1 1 0 100000000 0 0 50000

pclk_gpio2 1 1 0 100000000 0 0 50000

pclk_intr_arb 0 0 0 100000000 0 0 50000

pclk_grf 0 0 0 100000000 0 0 50000

pclk_uphy1_tcpd_g 0 0 0 100000000 0 0 50000

pclk_uphy1_tcphy_g 0 0 0 100000000 0 0 50000

pclk_uphy0_tcpd_g 0 0 0 100000000 0 0 50000

pclk_uphy0_tcphy_g 0 0 0 100000000 0 0 50000

pclk_usbphy_mux_g 0 0 0 100000000 0 0 50000

pclk_wdt 1 1 0 100000000 0 0 50000

gpll_hclk_perilp1_src 1 1 0 800000000 0 0 50000

hclk_perilp1 8 8 0 100000000 0 0 50000

hclk_sdioaudio_noc 1 1 0 100000000 0 0 50000

pclk_spi5 0 0 0 100000000 0 0 50000

hclk_sdio 1 3 0 100000000 0 0 50000

hclk_spdif 0 0 0 100000000 0 0 50000

hclk_i2s2 1 2 0 100000000 0 0 50000

hclk_i2s1 0 0 0 100000000 0 0 50000

hclk_i2s0 1 2 0 100000000 0 0 50000

hclk_sdio_noc 1 1 0 100000000 0 0 50000

hclk_perilp1_noc 1 1 0 100000000 0 0 50000

pclk_perilp1 5 7 0 50000000 0 0 50000

pclk_perilp1_noc 1 1 0 50000000 0 0 50000

pclk_perilp_sgrf 0 0 0 50000000 0 0 50000

pclk_spi4 0 0 0 50000000 0 0 50000

pclk_spi2 0 0 0 50000000 0 0 50000

pclk_spi1 0 0 0 50000000 0 0 50000

pclk_spi0 0 0 0 50000000 0 0 50000

pclk_efuse1024s 0 0 0 50000000 0 0 50000

pclk_efuse1024ns 0 0 0 50000000 0 0 50000

pclk_tsadc 1 1 0 50000000 0 0 50000

pclk_saradc 1 1 0 50000000 0 0 50000

pclk_mailbox0 0 0 0 50000000 0 0 50000

pclk_rki2c3 0 0 0 50000000 0 0 50000

pclk_rki2c2 0 0 0 50000000 0 0 50000

pclk_rki2c6 0 1 0 50000000 0 0 50000

pclk_rki2c5 0 0 0 50000000 0 0 50000

pclk_rki2c1 0 1 0 50000000 0 0 50000

pclk_rki2c7 0 0 0 50000000 0 0 50000

pclk_uart3 0 0 0 50000000 0 0 50000

pclk_uart2 1 1 0 50000000 0 0 50000

pclk_uart1 0 0 0 50000000 0 0 50000

pclk_uart0 0 0 0 50000000 0 0 50000

gpll_fclk_cm0s_src 1 1 0 800000000 0 0 50000

fclk_cm0s 1 1 0 266666667 0 0 50000

hclk_m0_perilp_noc 1 1 0 266666667 0 0 50000

clk_m0_perilp_dec 0 0 0 266666667 0 0 50000

dclk_m0_perilp 0 0 0 266666667 0 0 50000

hclk_m0_perilp 0 0 0 266666667 0 0 50000

sclk_m0_perilp 0 0 0 266666667 0 0 50000

clk_crypto0 0 0 0 100000000 0 0 50000

gpll_aclk_perilp0_src 2 2 0 800000000 0 0 50000

aclk_perilp0 5 6 0 266666667 0 0 50000

aclk_perilp0_noc 1 1 0 266666667 0 0 50000

aclk_dmac1_perilp 1 2 0 266666667 0 0 50000

aclk_dmac0_perilp 0 1 0 266666667 0 0 50000

aclk_dcf 0 0 0 266666667 0 0 50000

clk_intmem5 0 0 0 266666667 0 0 50000

clk_intmem4 0 0 0 266666667 0 0 50000

clk_intmem3 0 0 0 266666667 0 0 50000

clk_intmem2 0 0 0 266666667 0 0 50000

clk_intmem1 0 0 0 266666667 0 0 50000

clk_intmem0 0 0 0 266666667 0 0 50000

aclk_tzma 0 0 0 266666667 0 0 50000

aclk_intmem 0 0 0 266666667 0 0 50000

pclk_perilp0 2 2 0 44444445 0 0 50000

pclk_dcf 0 0 0 44444445 0 0 50000

hclk_perilp0 2 2 0 88888889 0 0 50000

hclk_perilp0_noc 1 1 0 88888889 0 0 50000

hclk_s_crypto1 0 0 0 88888889 0 0 50000

hclk_m_crypto1 0 0 0 88888889 0 0 50000

hclk_s_crypto0 0 0 0 88888889 0 0 50000

hclk_m_crypto0 0 0 0 88888889 0 0 50000

hclk_rom 0 0 0 88888889 0 0 50000

gpll_aclk_emmc_src 1 1 0 800000000 0 0 50000

aclk_emmc 2 4 0 100000000 0 0 50000

aclk_emmcgrf 0 0 0 100000000 0 0 50000

aclk_emmc_noc 2 2 0 100000000 0 0 50000

aclk_emmccore 0 0 0 100000000 0 0 50000

clk_emmc 1 2 0 200000000 0 0 50000

emmc_cardclock 0 0 0 200000000 0 0 50000

hclk_sd 2 2 0 200000000 0 0 50000

hclk_sdmmc_noc 1 1 0 200000000 0 0 50000

hclk_sdmmc 1 3 0 200000000 0 0 50000

gpll_aclk_perihp_src 2 2 0 800000000 0 0 50000

aclk_perihp 4 5 0 133333334 0 0 50000

aclk_perihp_noc 1 1 0 133333334 0 0 50000

aclk_pcie 0 0 0 133333334 0 0 50000

aclk_perf_pcie 0 0 0 133333334 0 0 50000

pclk_perihp 3 3 0 33333334 0 0 50000

pclk_hsicphy 0 0 0 33333334 0 0 50000

pclk_perihp_noc 1 1 0 33333334 0 0 50000

pclk_pcie 0 0 0 33333334 0 0 50000

pclk_perihp_grf 1 1 0 33333334 0 0 50000

hclk_perihp 6 6 0 66666667 0 0 50000

hclk_ahb1tom 0 0 0 66666667 0 0 50000

hclk_perihp_noc 1 1 0 66666667 0 0 50000

hclk_hsic 0 0 0 66666667 0 0 50000

hclk_host1_arb 2 4 0 66666667 0 0 50000

hclk_host1 2 4 0 66666667 0 0 50000

hclk_host0_arb 2 4 0 66666667 0 0 50000

hclk_host0 2 4 0 66666667 0 0 50000

aclk_center 2 2 0 400000000 0 0 50000

aclk_center_peri_noc 1 1 0 400000000 0 0 50000

aclk_center_main_noc 1 1 0 400000000 0 0 50000

gpll_cs 0 0 0 800000000 0 0 50000

gpll_cci_trace 0 0 0 800000000 0 0 50000

clk_cci_trace 0 0 0 133333334 0 0 50000

gpll_aclk_cci_src 0 0 0 800000000 0 0 50000

gpll_aclk_gmac_src 1 1 0 800000000 0 0 50000

aclk_gmac_pre 3 3 0 400000000 0 0 50000

pclk_gmac_pre 2 2 0 100000000 0 0 50000

pclk_gmac_noc 1 1 0 100000000 0 0 50000

pclk_gmac 2 4 0 100000000 0 0 50000

aclk_perf_gmac 0 0 0 400000000 0 0 50000

aclk_gmac_noc 1 1 0 400000000 0 0 50000

aclk_gmac 1 3 0 400000000 0 0 50000

clk_core_b_gpll_src 1 1 0 800000000 0 0 50000

clk_core_l_gpll_src 1 1 0 800000000 0 0 50000

clk_uphy1_tcpdcore 1 3 0 50000000 0 0 50000

clk_uphy0_tcpdcore 1 3 0 50000000 0 0 50000

pll_cpll 1 1 0 76299999 0 0 50000

cpll 1 1 0 76299999 0 0 50000

dclk_vop0_div 1 2 0 76299999 0 0 50000

dclk_vop0 1 2 0 76299999 0 0 50000

dclk_vop0_frac 0 0 0 3814999 0 0 50000

cpll_hclk_perilp1_src 0 0 0 76299999 0 0 50000

cpll_fclk_cm0s_src 0 0 0 76299999 0 0 50000

cpll_aclk_perilp0_src 0 0 0 76299999 0 0 50000

cpll_aclk_emmc_src 0 0 0 76299999 0 0 50000

cpll_aclk_perihp_src 0 0 0 76299999 0 0 50000

cpll_cs 0 0 0 76299999 0 0 50000

cpll_cci_trace 0 0 0 76299999 0 0 50000

cpll_aclk_cci_src 0 0 0 76299999 0 0 50000

cpll_aclk_gmac_src 0 0 0 76299999 0 0 50000

pll_dpll 0 0 0 856000000 0 0 50000

dpll 0 0 0 856000000 0 0 50000

clk_ddrc_dpll_src 0 0 0 856000000 0 0 50000

sclk_ddrc 0 0 0 856000000 0 0 50000

clk_core_b_dpll_src 0 0 0 856000000 0 0 50000

clk_core_l_dpll_src 0 0 0 856000000 0 0 50000

pll_bpll 0 0 0 1416000000 0 0 50000

bpll 0 0 0 1416000000 0 0 50000

clk_ddrc_bpll_src 0 0 0 1416000000 0 0 50000

clk_core_b_bpll_src 0 0 0 1416000000 0 0 50000

armclkb 0 0 0 1416000000 0 0 50000

aclkm_core_b 0 0 0 708000000 0 0 50000

aclk_perf_core_b 0 0 0 708000000 0 0 50000

aclk_core_adb400_core_b_2_cci500 0 0 0 708000000 0 0 50000

atclk_core_b 0 0 0 202285715 0 0 50000

pclk_dbg_core_b 0 0 0 202285715 0 0 50000

pclk_dbg_cxcs_pd_core_b 0 0 0 202285715 0 0 50000

pclken_dbg_core_b 0 0 0 50571429 0 0 50000

clk_dbg_pd_core_b 0 0 0 1416000000 0 0 50000

aclk_core_adb400_gic_2_core_b 0 0 0 1416000000 0 0 50000

aclk_core_adb400_core_b_2_gic 0 0 0 1416000000 0 0 50000

clk_core_l_bpll_src 0 0 0 1416000000 0 0 50000

pll_lpll 0 0 0 1416000000 0 0 50000

lpll 0 0 0 1416000000 0 0 50000

clk_ddrc_lpll_src 0 0 0 1416000000 0 0 50000

clk_core_b_lpll_src 0 0 0 1416000000 0 0 50000

clk_core_l_lpll_src 0 0 0 1416000000 0 0 50000

armclkl 0 0 0 1416000000 0 0 50000

aclkm_core_l 0 0 0 708000000 0 0 50000

aclk_perf_core_l 0 0 0 708000000 0 0 50000

aclk_core_adb400_core_l_2_cci500 0 0 0 708000000 0 0 50000

atclk_core_l 0 0 0 202285715 0 0 50000

pclk_dbg_core_l 0 0 0 202285715 0 0 50000

clk_dbg_pd_core_l 0 0 0 1416000000 0 0 50000

aclk_core_adb400_gic_2_core_l 0 0 0 1416000000 0 0 50000

aclk_core_adb400_core_l_2_gic 0 0 0 1416000000 0 0 50000

clk_pvtm_pmu 0 0 0 24000000 0 0 50000

clk_uart4_pmu 0 0 0 24000000 0 0 50000

clk_uart4_src 0 0 0 24000000 0 0 50000

clk_uart4_div 0 0 0 24000000 0 0 50000

clk_uart4_frac 0 0 0 1200000 0 0 50000

clk_32k_suspend_pmu 0 0 0 32743 0 0 50000

clk_timer_src_pmu 1 1 0 24000000 0 0 50000

clk_timer1_pmu 0 0 0 24000000 0 0 50000

clk_timer0_pmu 0 0 0 24000000 0 0 50000

pll_ppll 1 1 0 676000000 0 0 50000

ppll 3 5 0 676000000 0 0 50000

clk_crypto1 0 0 0 135200000 0 0 50000

pclk_pmu_src 5 7 0 48285715 0 0 50000

pclk_wdt_m0_pmu 0 0 0 48285715 0 0 50000

pclk_uart4_pmu 0 0 0 48285715 0 0 50000

pclk_mailbox_pmu 0 0 0 48285715 0 0 50000

pclk_timer_pmu 0 0 0 48285715 0 0 50000

pclk_spi3_pmu 0 0 0 48285715 0 0 50000

pclk_rkpwm_pmu 2 7 0 48285715 0 0 50000

pclk_i2c8_pmu 0 0 0 48285715 0 0 50000

pclk_i2c4_pmu 0 1 0 48285715 0 0 50000

pclk_i2c0_pmu 0 1 0 48285715 0 0 50000

pclk_noc_pmu 1 1 0 48285715 0 0 50000

pclk_sgrf_pmu 0 0 0 48285715 0 0 50000

pclk_gpio1_pmu 1 1 0 48285715 0 0 50000

pclk_gpio0_pmu 1 1 0 48285715 0 0 50000

pclk_intmem1_pmu 0 0 0 48285715 0 0 50000

pclk_pmugrf_pmu 0 0 0 48285715 0 0 50000

pclk_pmu 0 0 0 48285715 0 0 50000

clk_i2c8_pmu 0 0 0 169000000 0 0 50000

clk_i2c4_pmu 0 1 0 169000000 0 0 50000

clk_i2c0_pmu 0 1 0 169000000 0 0 50000

clk_wifi_div 0 0 0 26000000 0 0 50000

clk_wifi_pmu 0 0 0 26000000 0 0 50000

clk_wifi_frac 0 0 0 1300000 0 0 50000

clk_spi3_pmu 0 0 0 96571429 0 0 50000

fclk_cm0s_pmu_ppll_src 1 1 0 676000000 0 0 50000

fclk_cm0s_src_pmu 2 2 0 96571429 0 0 50000

hclk_noc_pmu 1 1 0 96571429 0 0 50000

dclk_cm0s_pmu 0 0 0 96571429 0 0 50000

hclk_cm0s_pmu 0 0 0 96571429 0 0 50000

sclk_cm0s_pmu 0 0 0 96571429 0 0 50000

fclk_cm0s_pmu 0 0 0 96571429 0 0 50000

pclkin_isp1_wrapper 0 0 0 0 0 0 50000

clk_pcie_core 0 0 0 0 0 0 50000

clk_i2s2_mux 0 1 0 0 0 0 50000

clk_i2s2 0 1 0 0 0 0 50000

clk_i2s1_mux 0 0 0 0 0 0 50000

clk_i2s1 0 0 0 0 0 0 50000

clk_i2s0_mux 1 1 0 0 0 0 50000

clk_i2s0 1 2 0 0 0 0 50000

clk_i2sout_src 1 1 0 0 0 0 50000

clk_i2sout 1 1 0 0 0 0 50000

clk_spdif_mux 0 0 0 0 0 0 50000

clk_spdif 0 0 0 0 0 0 50000

RK3399 Android 11 ES8316 驱动问题

异常日志

[ 72.884083] es8316 1-0010: No sysclk provided

[ 72.884123] es8316 1-0010: ASoC: can't open codec ES8316 HiFi: -22

[ 72.900928] es8316 1-0010: No sysclk provided

[ 72.900955] es8316 1-0010: ASoC: can't open codec ES8316 HiFi: -22

[ 72.917404] es8316 1-0010: No sysclk provided

[ 72.917427] es8316 1-0010: ASoC: can't open codec ES8316 HiFi: -22

[ 72.934706] es8316 1-0010: No sysclk provided

[ 72.934740] es8316 1-0010: ASoC: can't open codec ES8316 HiFi: -22

异常日志对应的时钟

cat /sys/kernel/debug/clk/clk_summary | egrep "i2s0|cpll"

dummy_cpll 0 0 0 0 0 0 50000

clk_i2s0_div 0 0 0 800000000 0 0 50000

clk_i2s0_frac 0 0 0 40000000 0 0 50000

hclk_i2s0 1 2 0 100000000 0 0 50000

pll_cpll 1 1 0 76299999 0 0 50000

cpll 1 1 0 76299999 0 0 50000

cpll_hclk_perilp1_src 0 0 0 76299999 0 0 50000

cpll_fclk_cm0s_src 0 0 0 76299999 0 0 50000

cpll_aclk_perilp0_src 0 0 0 76299999 0 0 50000

cpll_aclk_emmc_src 0 0 0 76299999 0 0 50000

cpll_aclk_perihp_src 0 0 0 76299999 0 0 50000

cpll_cs 0 0 0 76299999 0 0 50000

cpll_cci_trace 0 0 0 76299999 0 0 50000

cpll_aclk_cci_src 0 0 0 76299999 0 0 50000

cpll_aclk_gmac_src 0 0 0 76299999 0 0 50000

clk_i2s0_mux 1 1 0 0 0 0 50000

clk_i2s0 1 2 0 0 0 0 50000

android 7 正常日志对应的时钟

cat /sys/kernel/debug/clk/clk_summary | egrep "i2s0|cpll"

dummy_cpll 0 0 0 0 0

clk_i2s0_div 1 1 800000000 0 0

clk_i2s0_frac 1 1 11289600 0 0

clk_i2s0_mux 1 1 11289600 0 0

clk_i2s0 1 2 11289600 0 0

hclk_i2s0 1 2 100000000 0 0

pll_cpll 1 1 76299999 0 0

cpll 1 1 76299999 0 0

cpll_hclk_perilp1_src 0 0 76299999 0 0

cpll_fclk_cm0s_src 0 0 76299999 0 0

cpll_aclk_perilp0_src 0 0 76299999 0 0

cpll_aclk_emmc_src 0 0 76299999 0 0

cpll_aclk_perihp_src 0 0 76299999 0 0

cpll_cs 0 0 76299999 0 0

cpll_cci_trace 0 0 76299999 0 0

cpll_aclk_cci_src 0 0 76299999 0 0

cpll_aclk_gmac_src 0 0 76299999 0 0

修改方案

增加 system-clock-frequency = <11289600>; 配置

es8316-sound {

compatible = "simple-audio-card";

simple-audio-card,format = "i2s";

simple-audio-card,name = "rockchip,es8316-codec";

simple-audio-card,mclk-fs = <256>;

simple-audio-card,widgets =

"Microphone", "Mic Jack",

"Headphone", "Headphone Jack";

simple-audio-card,routing =

"Mic Jack", "MICBIAS1",

"IN1P", "Mic Jack",

"Headphone Jack", "HPOL",

"Headphone Jack", "HPOR";

simple-audio-card,cpu {

sound-dai = <&i2s0>;

system-clock-frequency = <11289600>;

};

simple-audio-card,codec {

sound-dai = <&es8316>;

system-clock-frequency = <11289600>;

};

};

0

次点赞